# MIPI 13C PHY

Revision1. 2

January 2022

Arasan Chip Systems Inc. 2150 N. 1st St. Suite 240, San Jose, CA 95131 Ph: 408-433-9633 www.arasan.com

#### Disclaimer

This document is written in good faith with the intent to assist the readers in the use of the product. Circuit diagrams and other information relating to Arasan Chip Systems' products are included as a means of illustrating typical applications. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. Information contained in this document is subject to continuous improvement and development.

Arasan Chip Systems' products are not designed, intended, authorized, or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. All such uses without prior written approval of an Officer of Arasan Chip Systems Inc. will be fully at the risk of the customer.

Arasan Chip Systems Inc. disclaims and excludes any and all warranties, including, without limitation, any and all implied warranties of merchantability, fitness for a particular purpose, title, and infringement and the like, and any and all warranties arising from any course or dealing or usage of trade.

This document may not be copied, reproduced, or transmitted to others in any manner. Nor may any use of information in this document be made, except for the specific purposes for which it is transmitted to the recipient, without the prior written consent of Arasan Chip Systems Inc. This specification is subject to change at any time without notice. Arasan Chip Systems Inc. is not responsible for any errors contained herein.

In no event shall Arasan Chip Systems Inc. be liable for any direct, indirect, incidental, special, punitive, or consequential damages; or for loss of data, profits, savings or revenues of any kind; regardless of the form of action, whether based on contract; tort; negligence of Arasan Chip Systems Inc or others; strict liability; breach of warranty; or otherwise; whether or not any remedy of buyers is held to have failed of its essential purpose, and whether or not Arasan Chip Systems Inc. has been advised of the possibility of such damages.

#### **Restricted Rights**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seg. or its successor.

#### **Copyright Notice**

No part of this specification may be reproduced in any form or means, without the prior written consent of Arasan Chip Systems, Inc.

Questions or comments may be directed to:

Arasan Chip Systems Inc. 2150 N 1st St. Suite 240, San Jose, CA 95131 Ph: 408-433-9633

Email: sales@arasan.com

# **Contents**

| 1 | Intro | oduction                      | 1  |

|---|-------|-------------------------------|----|

|   | 1.1   | About MIPI I3C                | 1  |

|   | 1.2   | Arasan's Contribution to MIPI | 1  |

|   | 1.3   | Arasan's Total IP™ Solution   | 1  |

| 2 |       | san's MIPI I3C PHY            |    |

|   |       | Arasan's MIPI I3C Host PHY    |    |

|   | 2.1.1 | Features                      | .3 |

|   | 2.1.2 |                               |    |

|   | 2.1.3 |                               |    |

|   | 2.1.4 |                               |    |

|   | 2.2   | Arasan's MIPI I3C Device PHY  | 5  |

|   | 2.2.1 |                               |    |

|   | 2.3   | SOC Level Integration         |    |

|   |       | IP Deliverables               |    |

|   |       |                               |    |

# **Figures**

| Figure 1Arasan's Total IP™ Solution                      | 2 |

|----------------------------------------------------------|---|

| Figure 2 Arasan's MIPI I3C Host PHY Block Diagram        | 3 |

| Figure 3 Arasan's MIPI I3C Device PHY Block Diagram      |   |

| rigule 3 Alasali S Iviiri isc device rat diuck diagrafii |   |

## 1 Introduction

### 1.1 About MIPI I3C

The I3C bus is used for various sensors in the mobile/automotive system where the Host transfers data and control between itself and various sensor devices. The I3C interface is intended to improve upon the features of the I2C interface, preserving backward compatibility. This I3C defines a standard multi-Drop interface between Host processors and peripheral Devices (e.g., sensors). Implementing the I3C Specification greatly increases the flexibility system designers have to supplant incumbent interfaces (i.e., I2C, SPI, UART) and support a wide array of Devices of increasing complexity and diversity in their system (e.g., sensor subsystem) and at as low a cost as possible.

### 1.2 Arasan's Contribution to MIPI

Arasan has been a member of MIPI for over ten years. We are active participants in several working groups. We work closely with other member customers to ensure compliant implementation of standards-based IP.

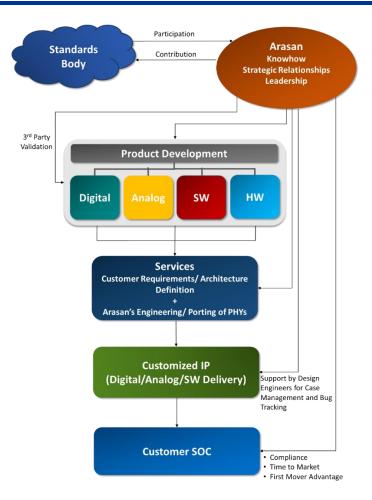

### 1.3 Arasan's Total IP™ Solution

Arasan provides a Total IP™ Solution, which encompasses all aspects of IP development and integration, including analog and digital IP cores, verification IP, software stacks & drivers, and hardware validation platforms. Benefits of Total IP™ Solution:

- Seamless integration from PHY to Software

- Assured compliance across all components.

- Single point of support

- Easiest acquisition process (one licensing source)

- Lowest overall cost including cost of integration.

- Lowest risk for fast time to market.

Figure 1Arasan's Total IP™ Solution

# 2 Arasan's MIPI I3C PHY

### 2.1 Arasan's MIPI I3C Host PHY

#### 2.1.1 Features

- Compliant with MIPI specification for I3C v1.1

- Supports DC operating parameters of both the modes: Open-drain & Push-Pull

- Higher speeds are achieved in Push-Pull mode using a totem pole driver in SDA

- Supports 1.8V/1.2 +/-10% supply for IOs and 0.8V +/-10% supply for the core.

#### 2.1.2 Architecture

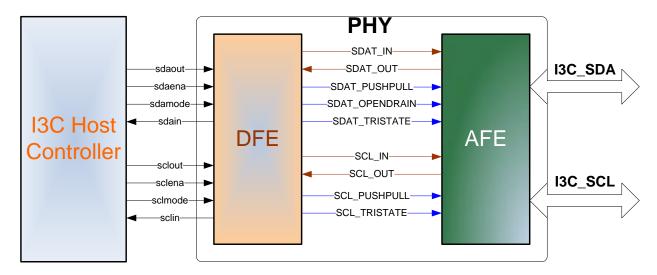

Figure below shows the block diagram of Arasan's MIPI I3C Host PHY and the Figure shows the Host PHY in detail.

Figure 2 Arasan's MIPI I3C Host PHY Block Diagram

### 2.1.3 **PIN List**

| PIN                                             | Direction                                                    | Description                                                   |  |  |  |  |

|-------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|

| Interface between Co                            | nterface between Controller/DFE (controller side IN and OUT) |                                                               |  |  |  |  |

| sdaout                                          | OUT                                                          | This is the output for the SDA Pin                            |  |  |  |  |

| sdaena                                          | OUT                                                          | This is the SDA control line enable                           |  |  |  |  |

| sdamode                                         | OUT                                                          | SDA Mode. 0: Open-Drain, 1-Push-pull                          |  |  |  |  |

| sdain                                           | IN                                                           | This is the input from the SDA Pin                            |  |  |  |  |

|                                                 |                                                              |                                                               |  |  |  |  |

| sclout                                          | OUT                                                          | This is the output for the SCL Pin.                           |  |  |  |  |

| sclena                                          | OUT                                                          | This is the SCL control line Enable                           |  |  |  |  |

| sclmode                                         | OUT                                                          | SCL Mode. 0: Open-Drain, 1-Push-pull                          |  |  |  |  |

| sclin                                           | IN                                                           | This is the clock from the SCL pin                            |  |  |  |  |

| Interface between DFE/AFE (AFE side IN and OUT) |                                                              |                                                               |  |  |  |  |

| sdat_in                                         | IN                                                           | Incoming data on SDA                                          |  |  |  |  |

| sdat_out                                        | OUT                                                          | Outgoing data on SDA                                          |  |  |  |  |

| sdat_OD                                         | IN                                                           | Active High signal indicates the SDA pad Open Drain operation |  |  |  |  |

| sdat_trist                                      | IN                                                           | Active high signal indicates the SDA pad tri state            |  |  |  |  |

| scl_in                                          | IN                                                           | Incoming Clock                                                |  |  |  |  |

| scl_out                                         | OUT                                                          | SCL Clock out                                                 |  |  |  |  |

| AFE Output                                      |                                                              |                                                               |  |  |  |  |

| I3C_SDAT                                        | INOUT                                                        | Bi-directional SDA – Data Lane                                |  |  |  |  |

| I3C_SCL                                         | INOUT                                                        | Bi-directional SCL – Clock Lane                               |  |  |  |  |

# 2.1.4 Power pins

| No | Pins  | Dir | Description             |

|----|-------|-----|-------------------------|

| 1  | VDDIO | 10  | Analog IO power pins    |

| 2  | VCORE | I   | Analog Core power pins  |

| 3  | GNDC  | 1   | Analog Core ground pins |

| 4  | VSSQ  | 10  | Analog IO ground pins   |

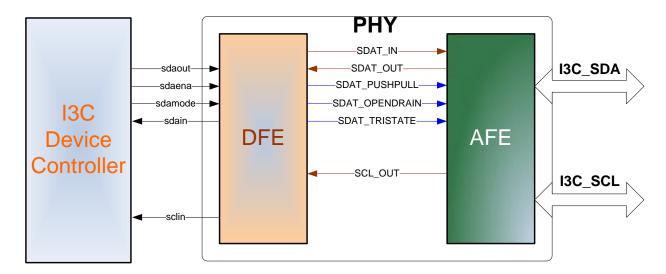

### 2.2 Arasan's MIPI I3C Device PHY

#### 2.2.1 Features

- Compliant with MIPI specification for I3C v1.1

- Supports DC operating parameters of both the modes: Open-drain & Push-Pull

- Higher speeds are achieved in Push-Pull mode using a totem pole driver in SDA

- Supports 1.8V/1.2 +/-10% supply for IOs and 0.8V +/-10% supply for the core.

Figure 3 Arasan's MIPI I3C Device PHY Block Diagram

# 2.3 SOC Level Integration

### 2.3.1 IP Deliverables

- GDSII

- CDL netlist for LVS

- LIB files

- LEF files

- Scan-inserted netlist with test guide

- Behavioral model with verification environment

- DRC and antenna reports

- Design integration guide

- User guide