# Datasheet

---

Total MIPI Camera IP Solution

CSI-2 v1.3 Transmitter Controller

CSI-2 v1.3 Receiver Controller

C-PHY v1.1 Physical Interface

D-PHY v1.2 Physical Interface

Arasan Chip Systems Inc.

2010 North First Street, Suite #510, San Jose, CA 95131

Ph: 408-282-1600

Fax: 408-282-7800

[www.arasan.com](http://www.arasan.com)

## Disclaimer

This document is written in good faith with the intent to assist the readers in the use of the product. Circuit diagrams and other information relating to Arasan Chip Systems' products are included as a means of illustrating typical applications. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. Information contained in this document is subject to continuous improvement and development.

Arasan Chip Systems' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Arasan Chip Systems Inc. will be fully at the risk of the customer.

Arasan Chip Systems Inc. disclaims and excludes any and all warranties, including, without limitation, any and all implied warranties of merchantability, fitness for a particular purpose, title, and infringement and the like, and any and all warranties arising from any course or dealing or usage of trade.

This document may not be copied, reproduced, or transmitted to others in any manner. Nor may any use of information in this document be made, except for the specific purposes for which it is transmitted to the recipient, without the prior written consent of Arasan Chip Systems Inc. This specification is subject to change at any time without notice. Arasan Chip Systems Inc. is not responsible for any errors contained herein.

In no event shall Arasan Chip Systems Inc. be liable for any direct, indirect, incidental, special, punitive, or consequential damages; or for loss of data, profits, savings or revenues of any kind; regardless of the form of action, whether based on contract; tort; negligence of Arasan Chip Systems Inc or others; strict liability; breach of warranty; or otherwise; whether or not any remedy of buyers is held to have failed of its essential purpose, and whether or not Arasan Chip Systems Inc. has been advised of the possibility of such damages.

## Restricted Rights

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

## Copyright Notice

No part of this specification may be reproduced in any form or means, without the prior written consent of Arasan Chip Systems, Inc.

Questions or comments may be directed to:

Arasan Chip Systems Inc.

2010 North First Street, Suite 510

San Jose, CA 95131

Ph: 408-282-1600

Fax: 408-282-7800

Email: [sales@arasan.com](mailto:sales@arasan.com)

## Contents

|          |                                                  |           |

|----------|--------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                              | <b>1</b>  |

| 1.1      | About CSI.....                                   | 1         |

| 1.2      | Arasan's Contribution to MIPI.....               | 1         |

| 1.3      | Arasan's Total IP Solution.....                  | 1         |

| <b>2</b> | <b>CSI-2 v1.3 Transmitter IP</b>                 | <b>3</b>  |

| 2.1      | Overview .....                                   | 3         |

| 2.2      | Features.....                                    | 3         |

| 2.3      | Architecture.....                                | 4         |

| 2.3.1    | Functional Description .....                     | 4         |

| 2.3.2    | Functional Block Diagram .....                   | 5         |

| 2.3.3    | Configuration-64-Bit Internal Data Bus.....      | 5         |

| 2.3.4    | Functional Block Diagram Description .....       | 7         |

| 2.4      | CSI-2 Combo Transmitter Pin Diagram .....        | 8         |

| 2.5      | SOC Level Integration.....                       | 8         |

| 2.5.1    | IP Deliverables.....                             | 8         |

| 2.5.2    | Verification Environment.....                    | 9         |

| <b>3</b> | <b>CSI-2 v1.3 Receiver IP</b>                    | <b>10</b> |

| 3.1      | Overview .....                                   | 10        |

| 3.2      | Features.....                                    | 10        |

| 3.3      | Architecture.....                                | 11        |

| 3.3.1    | Functional Description .....                     | 11        |

| 3.3.2    | Functional Block Diagram .....                   | 12        |

| 3.3.3    | Configuration – 64-Bit Internal Data Bus .....   | 12        |

| 3.3.4    | PHY Layer – DPHY.....                            | 12        |

| 3.3.5    | PHY Layer – C-PHY.....                           | 13        |

| 3.3.6    | Functional Block Diagram Description .....       | 14        |

| 3.4      | CSI-2 Combo Receiver Pin Diagram.....            | 17        |

| 3.5      | SOC Level Integration.....                       | 18        |

| 3.5.1    | IP Deliverables.....                             | 18        |

| 3.5.2    | Verification Environment.....                    | 18        |

| <b>4</b> | <b>C-PHY + D-PHY Combo Physical Interface IP</b> | <b>19</b> |

| 4.1      | Overview .....                                   | 19        |

| 4.2      | C-PHY Based Interconnect Architecture .....      | 19        |

| 4.3      | C-PHY Lane Architecture .....                    | 20        |

| 4.4      | D-PHY Based Interconnect Architecture .....      | 21        |

| 4.5      | C-PHY – D-PHY Pad Table .....                    | 21        |

|        |                                                                           |    |

|--------|---------------------------------------------------------------------------|----|

| 4.6    | Hard Macro Deliverables.....                                              | 34 |

| 5      | D-PHY v1.2 Physical Interface IP .....                                    | 35 |

| 5.1    | Overview .....                                                            | 35 |

| 5.2    | Features.....                                                             | 35 |

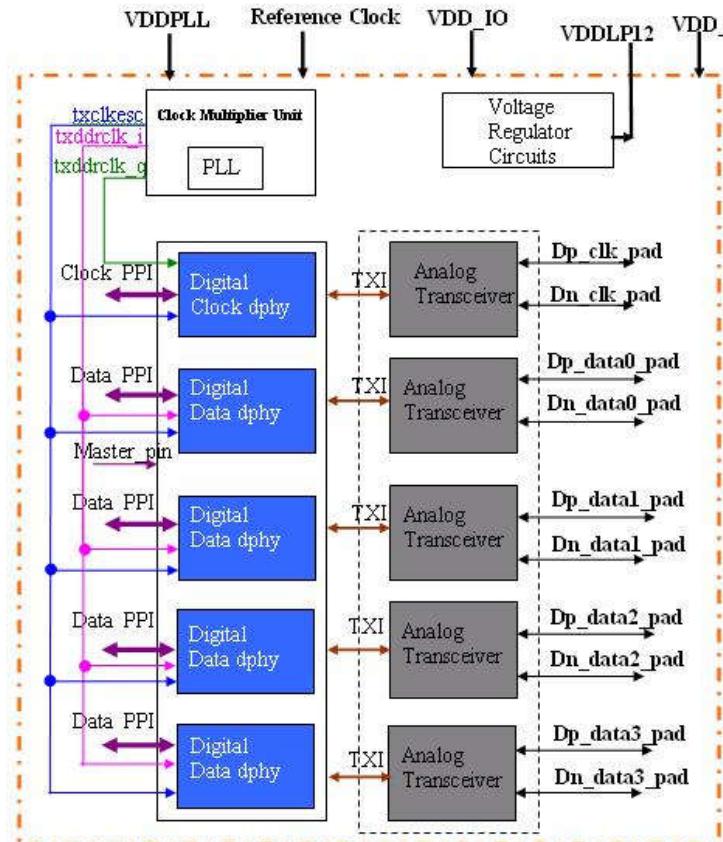

| 5.3    | Architecture.....                                                         | 36 |

| 5.3.1  | D-PHY Based Interconnect Architecture .....                               | 36 |

| 5.3.2  | D-PHY Lane Architecture.....                                              | 37 |

| 5.4    | Arasan D-PHY Architecture .....                                           | 38 |

| 5.5    | D-PHY Pad Table.....                                                      | 39 |

| 5.5.1  | Functional Description of D-PHY Pads for Clock Lane.....                  | 39 |

| 5.5.2  | Functional Description of D-PHY Pads for First Data Lane .....            | 39 |

| 5.5.3  | Functional Description of D-PHY Pads for Second Data Lane.....            | 39 |

| 5.5.4  | Functional Description of D-PHY Pads for Third Data Lane .....            | 39 |

| 5.5.5  | Functional Description of D-PHY Pads for Fourth Data Lane.....            | 40 |

| 5.5.6  | Power Pads.....                                                           | 40 |

| 5.5.7  | Functional Description of Trim Bits.....                                  | 40 |

| 5.5.8  | Functional Description of Clock and Reset Unit Input .....                | 41 |

| 5.5.9  | Functional Description of Data PPI Signals Common to all Data Lanes ..... | 41 |

| 5.5.10 | Functional Description of Clock PPI's Escape Mode Signals .....           | 41 |

| 5.5.11 | Functional Description of Clock PPI's Control Signals.....                | 42 |

| 5.5.12 | Functional Description of Clock PPI's High Speed Interface Signals .....  | 43 |

| 5.5.13 | Functional Description of Data PPI's Escape Mode Signals .....            | 44 |

| 5.5.14 | Functional Description of Data PPI's Control Signals.....                 | 45 |

| 5.5.15 | Functional Description of Side Band Signals .....                         | 46 |

| 5.5.16 | Functional Description of DFT Signals.....                                | 46 |

| 5.5.17 | D-PHY UI Parameter Count Signals .....                                    | 47 |

| 5.5.18 | A-BIST Related Signals.....                                               | 47 |

| 5.6    | Hard Macro Deliverables.....                                              | 48 |

| 6      | Services & Support .....                                                  | 49 |

| 6.1    | Global Support .....                                                      | 49 |

| 6.2    | Arasan Support Team.....                                                  | 49 |

| 6.3    | Professional Services & Customization .....                               | 49 |

| 6.4    | The Arasan Porting Engine .....                                           | 49 |

| 6.5    | Pricing & Licensing .....                                                 | 49 |

## Tables

|                                                                    |    |

|--------------------------------------------------------------------|----|

| Table 1: Functional description of D-PHY Pads for Clock Lane ..... | 21 |

| Table 2: Power Pads.....                                           | 22 |

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

| Table 3: Analog Function Trimming Inputs .....                                                     | 22 |

| Table 4: Clock and Reset Inputs .....                                                              | 23 |

| Table 5: Clock Lane High Speed PPI Interface Signals.....                                          | 24 |

| Table 6: Clock lane Escape PPI interface Signals.....                                              | 25 |

| Table 7: Clock lane PPI Control Signals .....                                                      | 26 |

| Table 8: Data lane High Speed PPI Interface Signals.....                                           | 26 |

| Table 9: Data lane Escape mode PPI Signals.....                                                    | 28 |

| Table 10: Data lane Escape Mode PPI Signals.....                                                   | 30 |

| Table 11: Data lane PPI Control Signals .....                                                      | 31 |

| Table 12: Side Band Signals.....                                                                   | 33 |

| Table 13: Clock Lane PPI Control Signals .....                                                     | 33 |

| Table 14: Functional Description of D-PHY Pads for Clock Lanes .....                               | 39 |

| Table 15: Functional Description of D-PHY Pads for First Data Lane.....                            | 39 |

| Table 16: Functional Description of D-PHY Pads for Second Data Lane .....                          | 39 |

| Table 17: Functional Description of D-PHY Pads for Third Data Lane .....                           | 39 |

| Table 18: Functional Description of D-PHY Pads for Fourth Data Lane .....                          | 40 |

| Table 19: Power Pads.....                                                                          | 40 |

| Table 20: Ports for Trim_Bits .....                                                                | 40 |

| Table 21: Functional Description of Clock and Reset unit Input signals for clock and data PPI..... | 41 |

| Table 22: Functional Description of data PPI signals that are common to all Data Lanes .....       | 41 |

| Table 23: Functional Description of Clock PPI's High Speed Interface Signals .....                 | 41 |

| Table 24: Functional Description of Clock PPI's Control Signals.....                               | 42 |

| Table 25: Functional Description of Data PPI's High Speed Interface signals.....                   | 43 |

| Table 26: Functional Description of Data PPI's Escape mode Signals.....                            | 44 |

| Table 27: Functional Description of Data PPI's Control Signals .....                               | 45 |

| Table 28: Functional Description of Side Band Signals .....                                        | 46 |

| Table 29: Functional Description of DFT Signals.....                                               | 46 |

| Table 30: D-PHY UI Parameter Count Signals .....                                                   | 47 |

| Table 31: A-BIST Pins.....                                                                         | 47 |

## Figures

|                                                                        |    |

|------------------------------------------------------------------------|----|

| Figure 1: Arasan's Total IP Solution .....                             | 2  |

| Figure 2: Combo Transmitter Functional Block Diagram.....              | 5  |

| Figure 3: Combo Transmitter Usage with 4-Lane D-PHY Version 1.2 .....  | 5  |

| Figure 4: Combo Transmitter Usage with 8-Lane D-PHY Version 1.2 .....  | 6  |

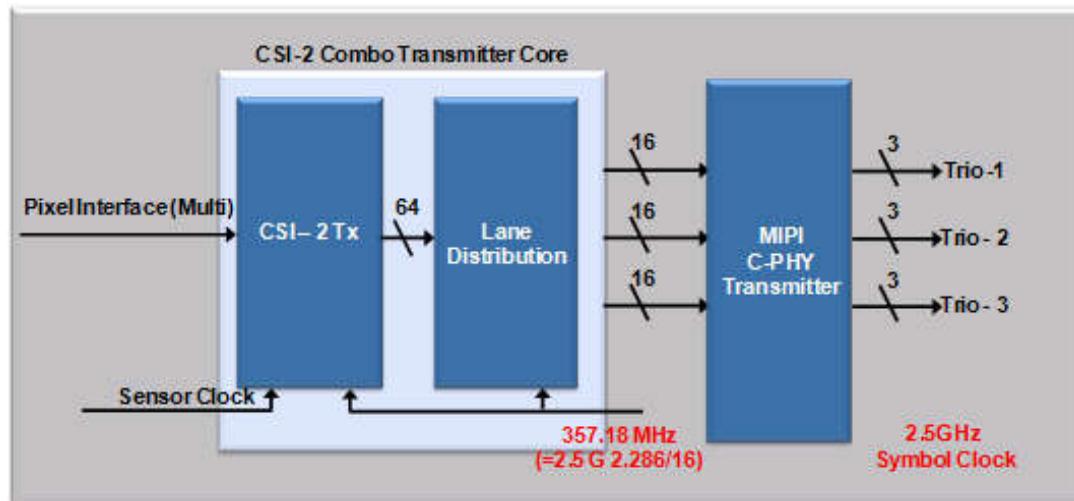

| Figure 5: Combo Transmitter Usage with 3-Lane C-PHY .....              | 6  |

| Figure 6: CSI-2 Combo Transmitter Pinout .....                         | 8  |

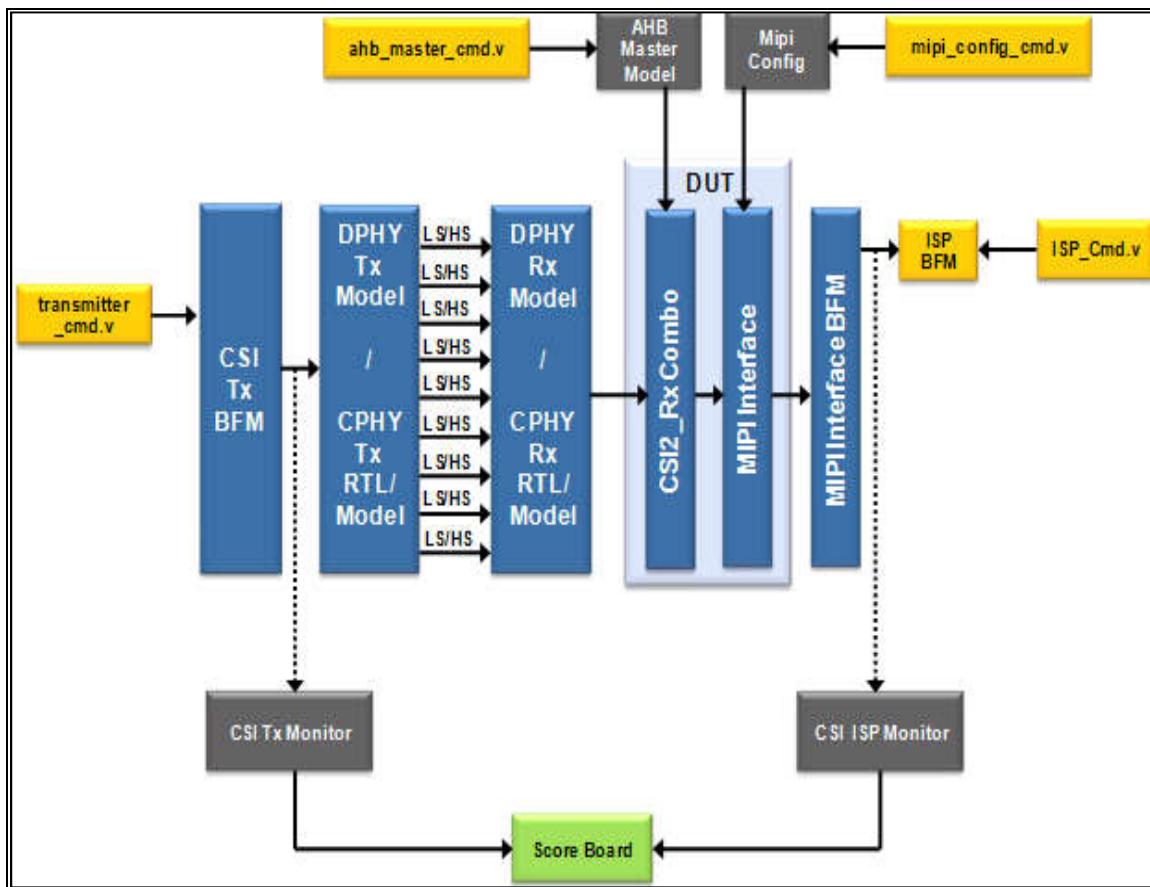

| Figure 7: Verification Environment of CSI-2 Combo Transmitter IP ..... | 9  |

| Figure 8: Functional Block Diagram .....                               | 12 |

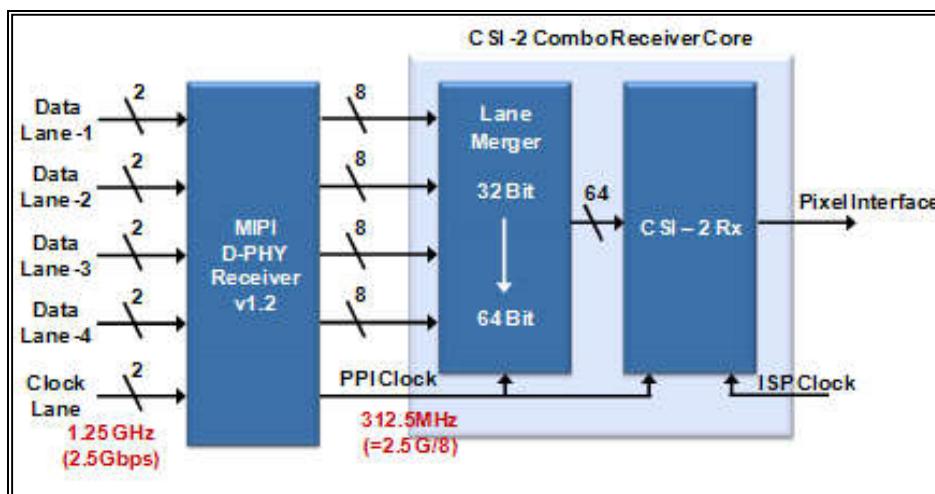

| Figure 9: Combo Receiver Usage with 4 Lane D-PHY V 1.2 .....           | 12 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

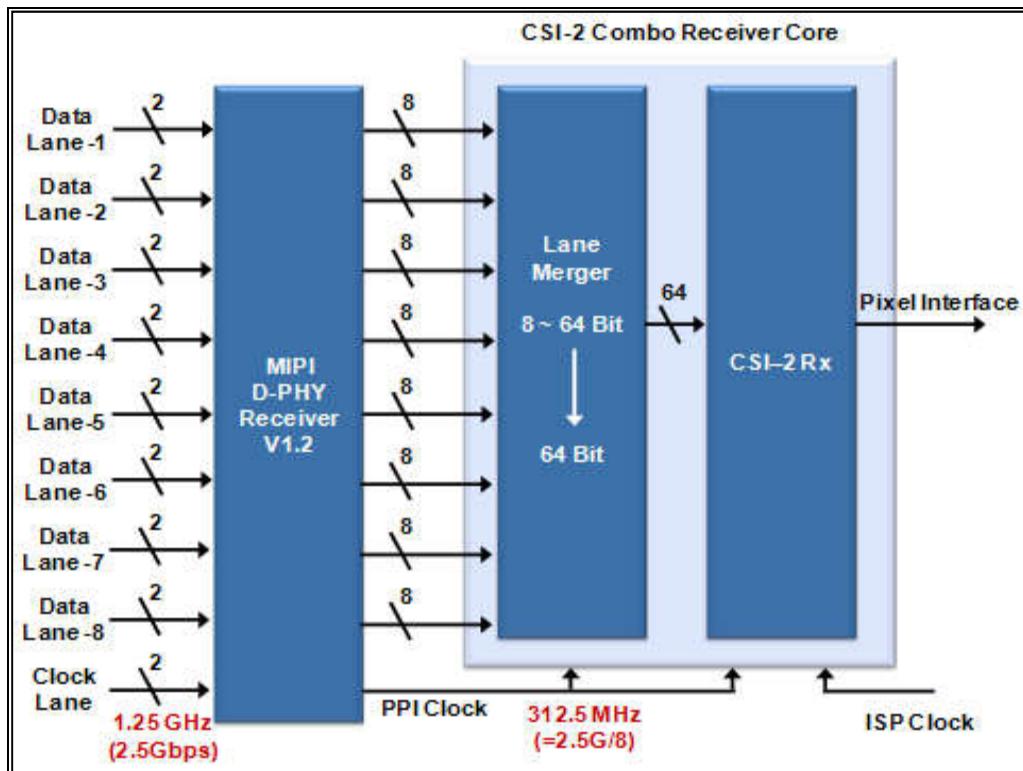

| Figure 10: Combo Receiver Usage with 8 Lane D-PHY V 1.2 .....      | 13 |

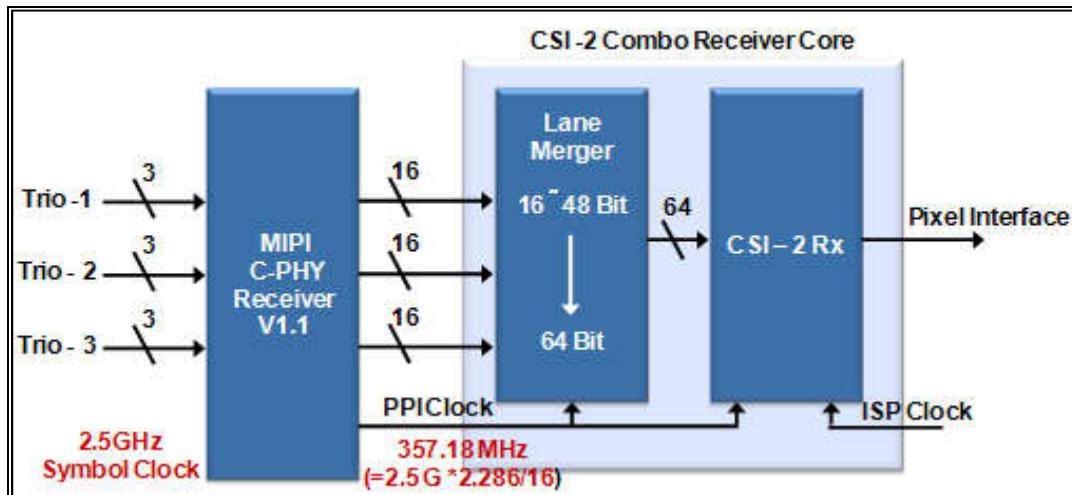

| Figure 11: CSI-2 Combo Receiver Usage with 3 Lane C-PHY V 1.2..... | 13 |

| Figure 12: CSI-2 Receiver Combo PIN Diagram.....                   | 17 |

| Figure 13: Verification Environment of CSI-2 Receiver IP.....      | 18 |

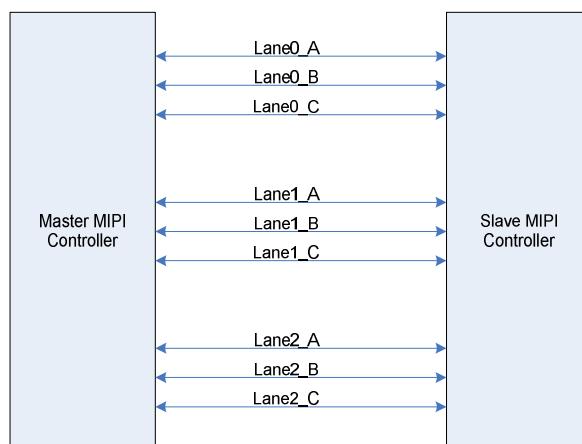

| Figure 14: MIPI Link Diagram for CPHY.....                         | 19 |

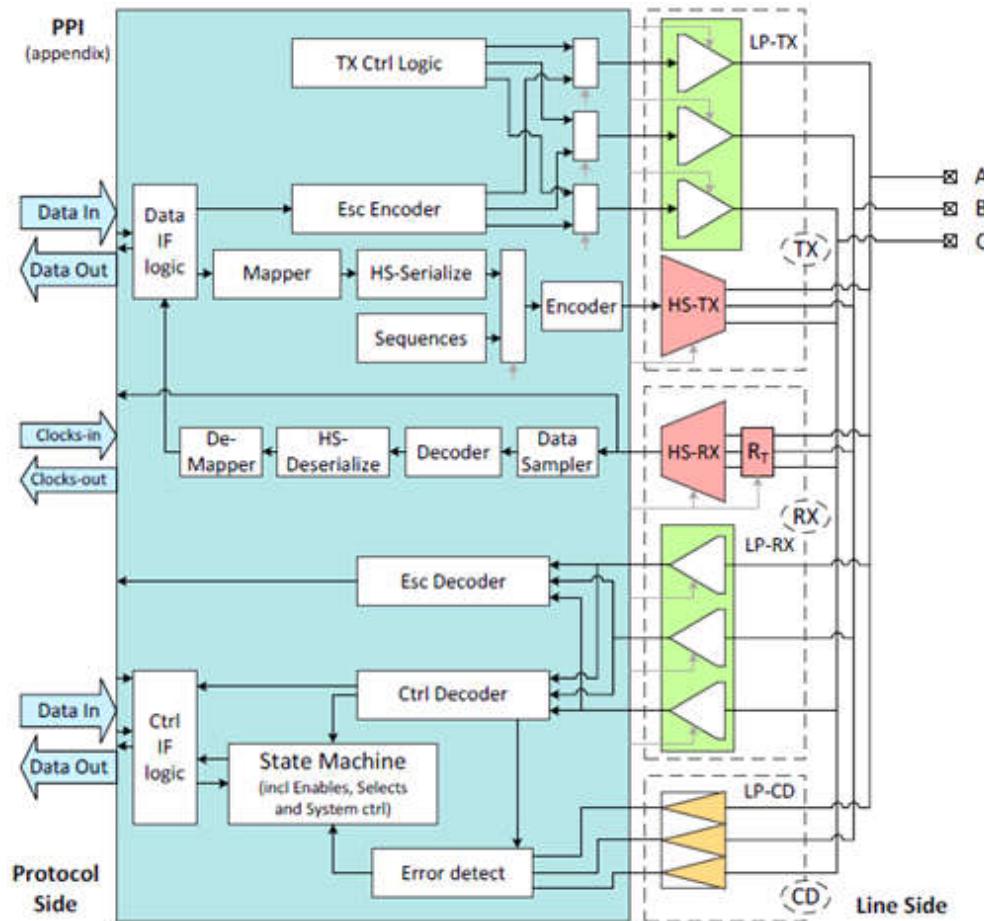

| Figure 15: C-PHY Lane Architecture .....                           | 20 |

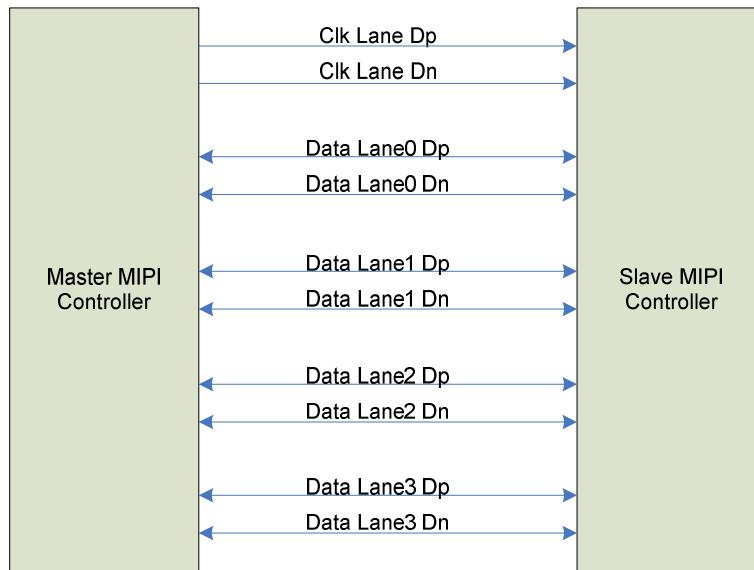

| Figure 16: MIPI Link Diagram for DPHY.....                         | 21 |

| Figure 25: MIPI Link Diagram for Four Data Lanes .....             | 36 |

| Figure 26: D-PHY Lane Architecture.....                            | 37 |

| Figure 27: Analog and Digital D-PHY Block Diagram.....             | 38 |

# 1 Introduction

## 1.1 About CSI

The MIPI® Alliance the Camera Serial Interface (CSI-2) dates back to November 2005 and was in widespread use in consumer devices by 2009. CSI-2 V1.1 was approved in January 2013. CSI-2 v1.2 was released in September 2014. The updated version, CSI-2 v1.3 (covered in this document) was released in February 2015.

Demand for increasingly higher image resolutions is pushing the bandwidth capacity of existing host processor-to-camera sensor interfaces. Common parallel interfaces are difficult to expand, require many interconnects and consume relatively large amounts of power. Emerging serial interfaces address many of the shortcomings of parallel interfaces while introducing their own problems. Incompatible, proprietary interfaces prevent devices from different manufacturers from working together. This can raise system costs and reduce system reliability by requiring “hacks” to force the devices to interoperate. The lack of a clear industry standard can slow innovation and inhibit new product market entry.

CSI-2 provides the mobile industry a standard, robust, scalable, low-power, high-speed, cost-effective interface that supports a wide range of imaging solutions for mobile devices.

## 1.2 Arasan's Contribution to MIPI

Arasan has been a member of MIPI for over ten years. We are active participants in a number of working groups. We work closely with other member customers to ensure compliant implementation of standards based IP.

## 1.3 Arasan's Total IP Solution

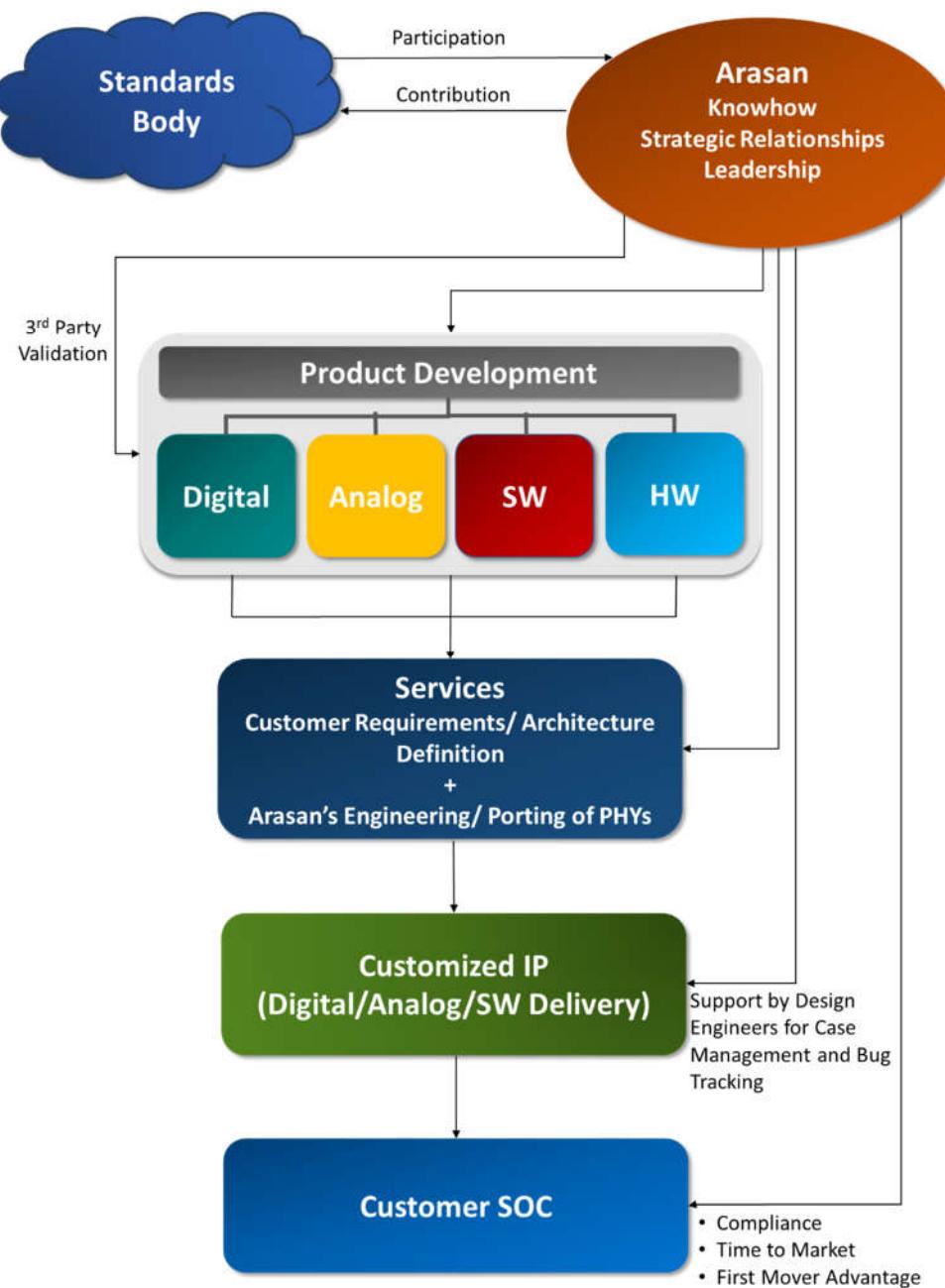

Arasan provides a Total IP Solution, which encompasses all aspects of IP development and integration, including analog and digital IP cores, verification IP, software stacks & drivers, and hardware validation platforms. Benefits of Total IP Solution:

- Seamless integration from PHY to Software

- Assured compliance across all components

- Single point of support

- Easiest acquisition process (one licensing source)

- Lowest overall cost including cost of integration

- Lowest risk for fast time to market

Figure 1: Arasan's Total IP Solution

## 2 CSI-2 v1.3 Transmitter IP

### 2.1 Overview

Arasan Chip Systems is a leading SOC IP provider of a complete suite of MIPI compliant IP solutions, which consist of IP cores, verification IP, software stacks and drivers, protocol analyzers, hardware platforms for software development and compliance testing, and optional customization services.

The MIPI compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms. This leads to smaller footprint, greater interoperability between mobile IP, chips and devices from diverse sources, and lower power and EMI.

This document describes the Arasan IP Core that functions as a MIPI CSI-2 Transmitter, which typically resides in a mobile platform's camera module, and communicates over a D-PHY/C-PHY link to a CSI2 Receiver in the applications processor. The Arasan CSI-2 combo IP is MIPI-compliant and provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

### 2.2 Features

- Compliant with the following MIPI specifications:

- [mipi\\_CSI-2\\_specification\\_v1-3](#)

- [mipi\\_CSI-2\\_specification\\_v1-2](#)

- [mipi\\_D-PHY\\_specification\\_v1-2](#)

- [mipi\\_C-PHY\\_specification\\_v1-0](#)

- CSI-2 Combo Transmitter Core features:

- Use of either D-PHY/C-PHY by user configuration

- Lane Configurability depending on the bandwidth requirements of the application, up to 8-lanes for DPHY and up to 4-lanes for C-PHY

- Connectivity to DPHY/CPHY through MIPI PPI Interface

- High Speed (HS) transmit rates of 182Mbps to 5714Mbps per lane with C-PHY interface

- High Speed (HS) transmit rates of 40Mbps to 2500Mbps per lane with D-PHY interface

- Support for Ultra Low Power Mode (ULPS)

- Support for Continuous and Non-Continuous Clock Mode

- Pixel formats supported

- [RAW data type](#)

- [YUV data type](#)

- [RGB data type](#)

- [All user Defined data types / JPEG](#)

- [Generic 8-bit long packet data types](#)

- Supports Data Type Interleaving

- Supports Virtual Channel Interleaving

- Pixel Level Input Interface for Image Sensor

- Supports Header and Payload Checksum

- Configurable for two mode of operation

- Store and Forward Mode – Stores the full pixel packet before forwarding.

- Cut through Mode – Initiates the HS transmission to D/CPHY as soon as the pixel information is received. Makes use of very shallow memory.

- Supports Multi Pixel Mode – Multiple Pixels per clock to bring down the sensor clock frequency to support higher resolution applications

- PPI Data Lane swapping as per user configuration

- Optional support for Compressed data formats

- Host interface for register configuration and monitoring,

- Used for programming both CSI-2 and PHY related registers. Reserved address space [0x00 – 0x0F] for the PHY related registers.

- Optional support for the AHB/APB/Microcontroller Interface

## 2.3 Architecture

### 2.3.1 Functional Description

The Arasan CSI-2 Transmitter IP is designed to provide MIPI CSI-2 v1-2/ CSI-2 v1-3 compliant high speed serial connectivity for camera modules in mobile platforms. Serial connectivity between this IP to the mobile applications processor's CSI-2 Receiver is implemented using 1 to 8 D-PHY Lanes (or) 1 to 6 C-PHY lanes, depending on camera sensor resolutions and the resulting bandwidth needs. This IP connects to the D-PHY/CPHY through the PPI interface. The PPI interface of the IP is compliant to MIPI `mipi_D-PHY_specification_v1-2/mipi_C-PHY_specification_v1-0`. The usage of PHY's is selected by simple programming based on the use case.

Initial configuration of this IP and its associated D-PHY/C-PHY can be done through programmed IO over an AHB/APB bus. However, other bus interface can be provided upon request.

Pixel Data received from over the Camera Sensor Bus is packed into bytes by the Transmitter IP. The packing of the pixel into bytes follows the CSI-2 spec and based on the pixel format support. This IP calculated and appends an ECC/CRC value to a short packet (or) to the header of a long packet. Selection of ECC/CRC to the header is done based on the PHY connected. For the payload of a long packet carrying pixel data, this IP calculates its CRC value and appends to the packet as a Packet Footer (PF). The packet is buffered in a FIFO and sent to one or more D-PHY/C-PHY depending on the lane distribution scheme set by the camera sensor/user.

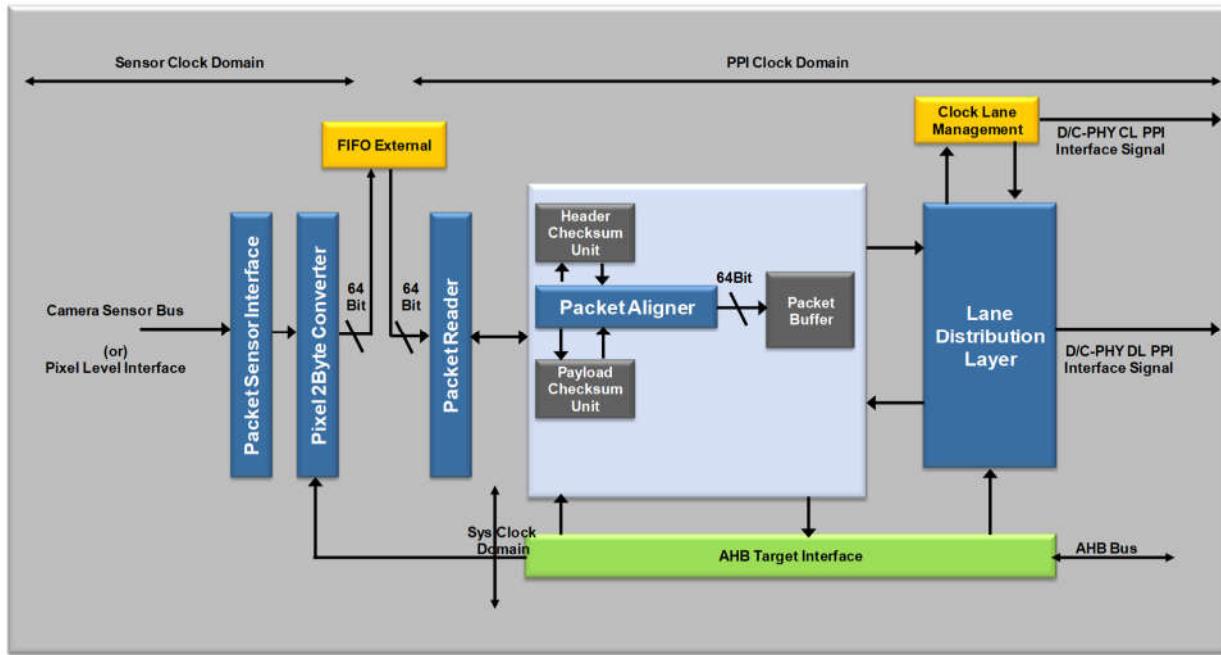

## 2.3.2 Functional Block Diagram

Figure 2: Combo Transmitter Functional Block Diagram

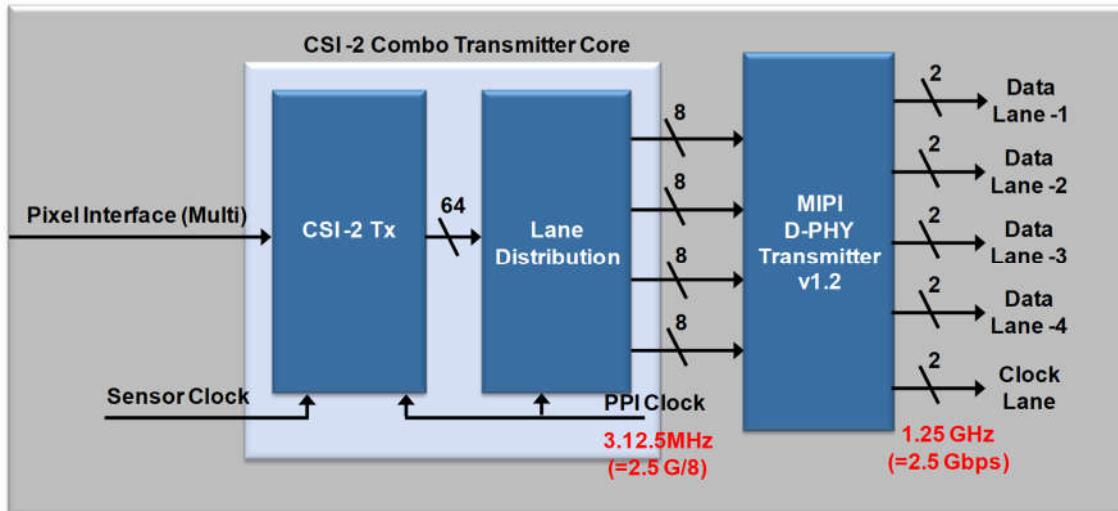

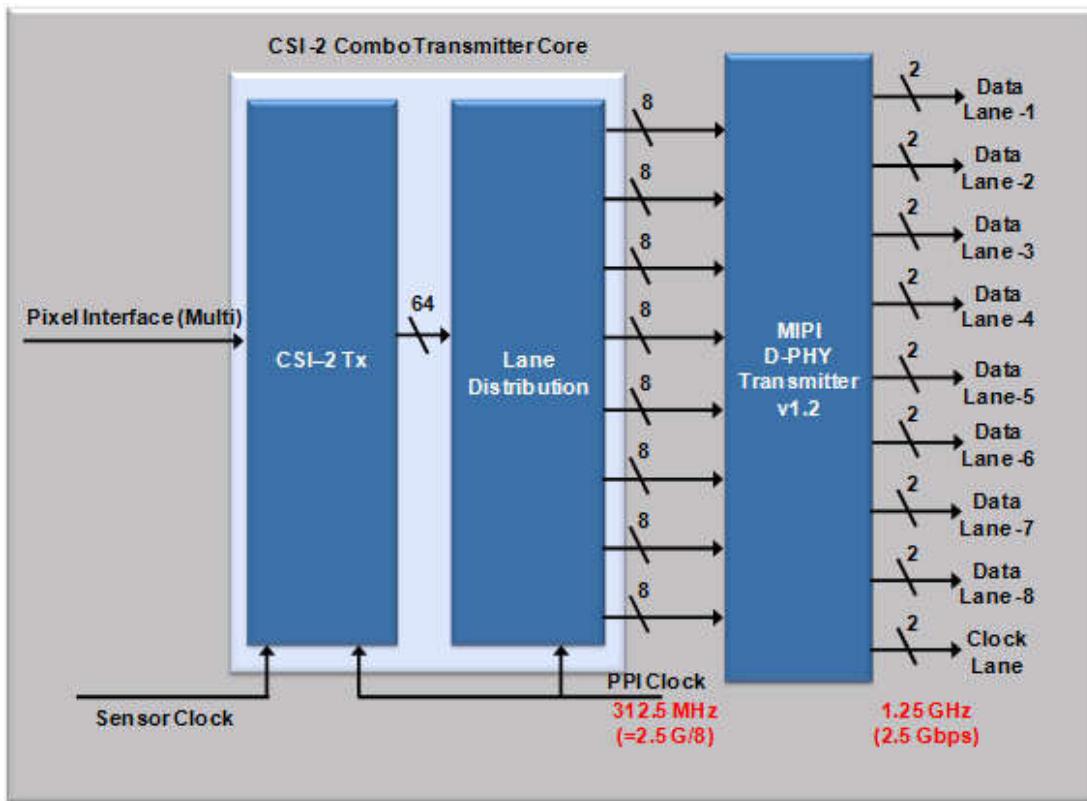

## 2.3.3 Configuration-64-Bit Internal Data Bus

The IP can be programmed to use with following configuration, when the internal data bus is 64-bit.

### 2.3.3.1 PHY Layer -DPHY

**Note:** The frequency of sensor clock can vary as long as the FIFO does not underflow and depends on the pixel mode/clock configuration.

Figure 3: Combo Transmitter Usage with 4-Lane D-PHY Version 1.2

Figure 4: Combo Transmitter Usage with 8-Lane D-PHY Version 1.2

### 2.3.3.2 PHY Layer -CPHY

Figure 5: Combo Transmitter Usage with 3-Lane C-PHY

## 2.3.4 Functional Block Diagram Description

### 2.3.4.1 AHB Target Interface

This module connects the CSI-2 Transmitter core to external AHB processor. The user can configure the different application specific attributes through set of registers. The user can program the lanes, pixel mode and also can get status information's like FIFO status, ULPS status etc. This can be used to program both CSI-2 and PHY related registers.

### 2.3.4.2 Packet Sensor Interface

This module interfaces to external sensor. The module provides a handshake mechanism to accept the long pixel data packet and the synchronization packets like Frame Start (FS), Line Start (LS), Line End (LE) and Frame End (FE). This also controls the data flow from the external sensor interface to the CSI-2 Combo Transmitter Controller.

### 2.3.4.3 Pixel to Byte Convertor

This module converts the received pixel information to byte as per the CSI-2 specification. The respective pixel to byte convertor will get enabled based on the received data type. This module converts the received pixel information and sync packet information to 64-bit and forwards it to external memory. This module also takes care of compression of pixel information.

### 2.3.4.4 FIFO

This is library specific dual Port (or) Two Port RAM, which is instantiated outside the CSI-2 IP. This is used as temporary storage buffer. The size of the buffer would vary based on the application.

In cut-through mode application, which makes use of very shallow memory, this FIFO could be replaced with the register based memory. However, for store and forward architectures the size of the memory varies with the size of the resolution required. Usually for store and forward the size of the FIFO should be  $2 * \text{MAX Line size required}$ .

### 2.3.4.5 Packet Reader

This module keeps track the number of packet to be processed. In cut-through mode applications, initiates the read as per the required threshold for the respective data format. Whereas in store and forward mechanism, this module waits for the complete packet to be stored in the FIFO before forwarding it to the low level protocol layer for further processing.

### 2.3.4.6 Low Level Protocol

This module based on the packet format received calculates the ECC/CRC for header and frames the packet header. For the received payload, calculates the CRC and appends it to the packet as packet footer.

### 2.3.4.7 Lane distribution Layer

This module takes care of the bytes/word distribution on to different D-PHY/C-PHY data lanes based on the user lane configuration. This will provides the PPI interface for the D-PHY/C-PHY. The clock lane layer manages the Clocks Lane PPI interface for D-PHY/C-PHY

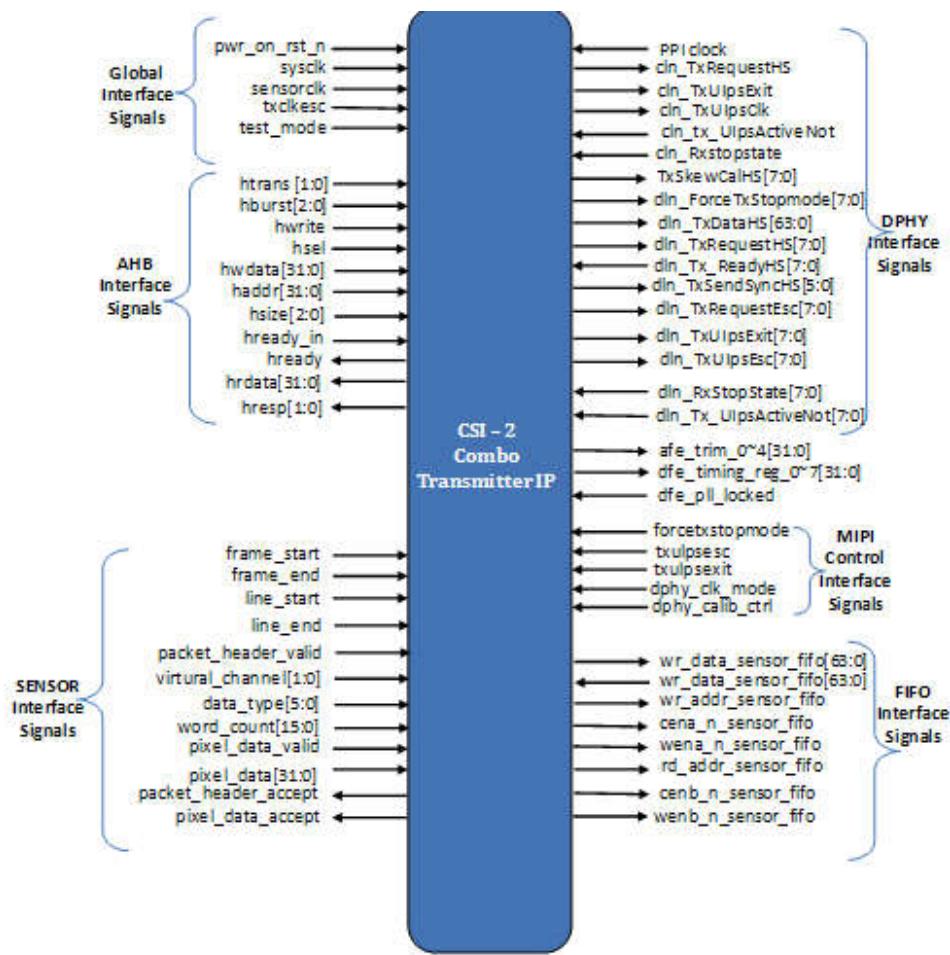

## 2.4 CSI-2 Combo Transmitter Pin Diagram

**Note:**

1. Based on the configuration/PHY selected only fewer bits of PPI signals are used.

Figure 6: CSI-2 Combo Transmitter Pinout

## 2.5 SOC Level Integration

### 2.5.1 IP Deliverables

- Verilog HDL of the IP core

- User guide

- Synthesis scripts

- Lint report

- CDC report

- Verilog test suite

- Gate count estimation available upon request

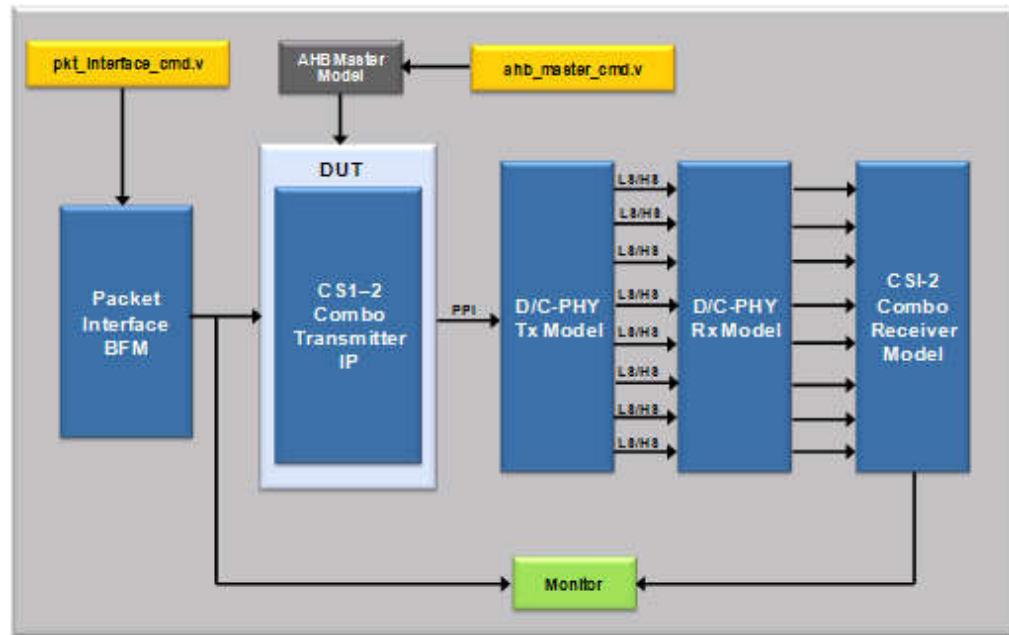

## 2.5.2 Verification Environment

Figure 7: Verification Environment of CSI-2 Combo Transmitter IP

## 3 CSI-2 v1.3 Receiver IP

### 3.1 Overview

Arasan Chip Systems is a leading System on Chip (SoC) Intellectual Property (IP) provider of a complete suite of Mobile Industry Processor Interface (MIPI) compliant IP solutions, which consists of IP cores, verification IP, software stacks and drivers, protocol analyzers, hardware platforms(HVP's) for software development and compliance testing and optional customization services.

The Mobile Connectivity (MIPI) compliant IP cores are interface building blocks that simplify interconnect architectures in mobile platforms. This leads to smaller footprint, greater interoperability between mobile IP, chips and devices from diverse sources and lower power and Electro Magnetic Interface (EMI).

This document describes the Arasan IP Core that functions as a MIPI Camera Serial Interface (CSI-2 Combo) Receiver, which interfaces between a peripheral device (Camera module) and a host processor (baseband, application engine). The CSI-2 Combo Receiver IP communicates over a D-PHY (or) C-PHY serial link to image processing block, part of the application engine. The Arasan CSI-2 combo IP is MIPI compliance and provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

### 3.2 Features

- Compliant with the following MIPI specifications

- `mipi_CSI-2_specification_v1-3`

- `mipi_CSI-2_specification_v1-2`

- `mipi_D-PHY_specification_v1-2`

- `mipi_C-PHY_specification_v1-0`

- CSI-2 Combo Receiver Core features:

- Use of either D-PHY/C-PHY by user configuration

- Different Configuration allowed for multiple use cases,

- 4-Lane/8-Lane D-PHY / 3-Lane C-PHY

- Lane Configurability depending on the bandwidth requirements of the application, up to 8-lanes for DPHY and up to 4-lanes for C-PHY

- High Speed (HS) receiver rates of 182Mbps to 5714Mbps per lane with C-PHY interface

- High Speed (HS) receiver rates of 40Mbps to 2500Mbps per lane with D-PHY interface

- Supports for Ultra Low Power Mode (ULPS)

- Single (or) Optional Multi-Pixel mode interface to ISP. The multi-pixel mode is used in high bandwidth requirement applications to lower the ISP clock frequency requirement.

- Optional Pixel Level Interface to ISP with HSYNC, VSYNC, DATA and DATA VALID

- Streams the received pixels onto eight data channels(customizable) based on the channel configurability from ISP

- Separate data channel for the short generic packets

- Support for all packet level errors, Protocol Decoding Level errors

- Support for cut-through (or) store and forward mode. Cut-through mode makes use of shallow Memory for memory critical applications.

- Optional support for Compressed data formats

- Optional support for different error counting

- Pixel formats supported

- RAW data type – RAW8, RAW10, RAW12, RAW14

- YUV data type – YUV422-8bit, YUV422-10bit

- RGB data type – RGB888, RGB666, RGB565, RGB555, RGB444

- All user Defined data types / JPEG

- Generic 8-bit long packet data types

- Host interface for register configuration and monitoring,

- Used for programming both CSI-2 and PHY related registers. Reserved address space [0x00 – 0x0F] for the PHY related registers.

- Optional support for the AHB/APB/Microcontroller Interface

## 3.3 Architecture

### 3.3.1 Functional Description

The Arasan CSI-2 Receiver IP is designed to provide MIPI CSI-2 v1-2/ CSI-2 v1-3 compliant high speed serial connectivity for application processors to corresponding camera modules in mobile platforms. Serial connectivity between this IP and an external camera module's CSI-2 transmitter is implemented using 1 to 8 D-PHY Lanes (or) 1 to 6 C-PHY lanes, depending on camera sensor resolutions and the application bandwidth needs. This IP connects to the D-PHY/CPHY through the PPI interface. The PPI interface of the IP is compliant to MIPI `mipi_D-PHY_specification_v1-2/mipi_C-PHY_specification_v1-0`. The usage of PHY's is selected by simple programming based on the use case.

Initial configuration of this IP and its associated D-PHY/C-PHY can be done through programmed IO over an AHB/APB bus. However, other bus interface can be provided upon request.

This IP performs the data lane merging of pixel data received on the PPI interface. It performs CRC and ECC checks to ensure the integrity of the packet payload and the header. Based on the PHY connected, lanes are merged accordingly and respective checks will be performed automatically. As per the application setting, IP either forwards (or) drops the erroneous packets. All forwarded packet payloads are then converted from byte to respective pixel format and output to an Image Signal Processor of the applications processor's graphics sub-system. A simple Pixel Level Interface

is used to forward the pixel information. All PHY level errors, packet level errors and decoding level errors are communicated to the HOST.

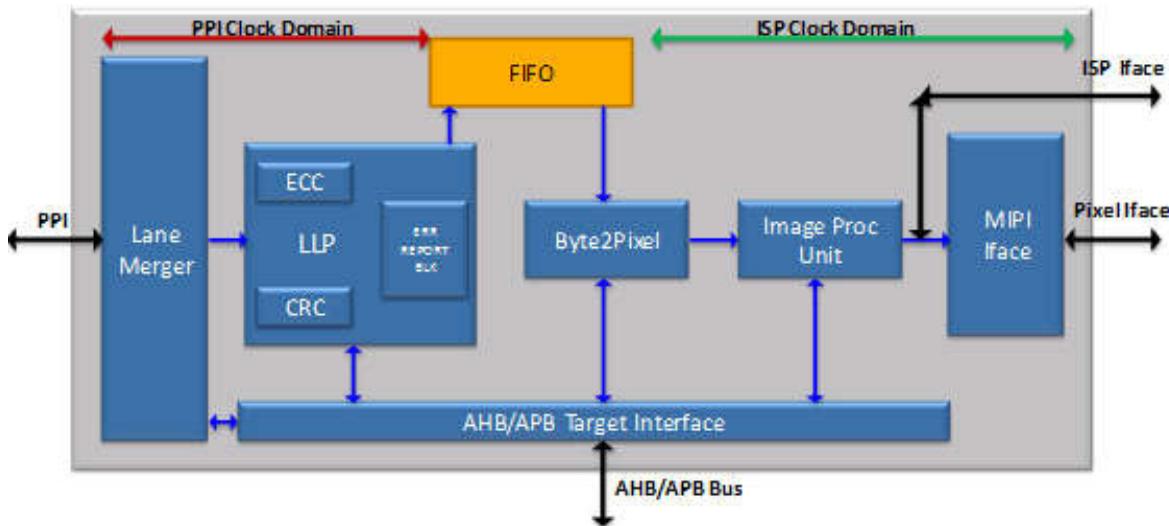

### 3.3.2 Functional Block Diagram

Figure 8: Functional Block Diagram

### 3.3.3 Configuration – 64-Bit Internal Data Bus

The IP can be programmed to use with following configuration, when the internal data bus is 64-bit.

### 3.3.4 PHY Layer – DPHY

The CSI-2 Combo Receiver IP can be used to configure number of lanes from 1 to 8.

**Note:** - The frequency of ISP clock can vary as long as the FIFO does not overflow and depends on the pixel mode/clock configuration.

Figure 9: Combo Receiver Usage with 4 Lane D-PHY V 1.2

Figure 10: Combo Receiver Usage with 8 Lane D-PHY V 1.2

### 3.3.5 PHY Layer – C-PHY

Figure 11: CSI-2 Combo Receiver Usage with 3 Lane C-PHY V 1.2

### 3.3.6 Functional Block Diagram Description

#### 3.3.6.1 AHB Target Interface

This module connects the CSI-2 Receiver core to external AHB processor. The user can configure the different application specific attributes through set of registers. The user can program the lanes, pixel mode and also can get status information's like PHY level information, Packet level error information etc. This can be used to program both CSI-2 and PHY related registers.

#### 3.3.6.2 Lane Merger

The CSI-2 Receiver is lane-scalable for increased performance. The number of data lanes may be chosen depending on the bandwidth requirement of the application. This module collects the bytes from the lanes programmed and merges them together into a recombined data stream that restores the original stream sequence. On merging the bytes, forward the stream to LLP layer for further processing. This module also handles the inter lane skew for the C-PHY application.

#### 3.3.6.3 Low Level Protocol Unit

This module determines if the received packet is of type short (or) long. For long packets, a CRC check is performed on the payload by comparing a calculated checksum on the payload with the checksum received with packet. If connected PHY is D-PHY, an ECC check is performed on the header, single-bit errors are corrected and 2-bit errors are detected. If connected PHY is C-PHY, a CRC is performed on header received. This module also checks for all type of protocol and decoding level errors. This module takes care of interrupt generation for the critical decisions from the application. Depending on the application/use case settings, this block decides whether to forward (or) drop the erroneous packets.

#### 3.3.6.4 FIFO

The FIFO module is used to synchronize the data flow from the LLP clock domain to ISP's clock domain. The FIFO size is configurable based on the user requirement. The FIFO size is based on the mode of operation chosen for the application. The Receiver IP adopts cut-through (or) store and forward functional modes. The cut-through requires a very shallow memory and for store and forward, memory size varies with the use case. For application, which makes use of 1 to 8 lanes DPHY and 1 to 3- lanes C-PHY, the width of the FIFO would be 64-bit. However for other configuration (6-lane C-PHY) the FIFO width required would be 96-bit. Depending on the IP configuration, the internal data bus will get change

#### 3.3.6.5 Byte2Pixel Unit

This module unpacks the received byte stream to pixel format with respect to received data type. This module takes care of enabling respective pixel unit.

To ensure compatibility with camera modules that support data compression on RAW data types, this unit implements the two prediction and the six decompression schemes specified in the CSI-2 standard. This feature is optional and is register programmable.

### 3.3.6.6 Image Processor Unit

This module further processes the received pixel information and packs them into multiple pixels based on the user configuration. For high resolution application, the requirement of higher ISP clock can be reduced by adopting the multi-pixel (more than one pixel per clock) mode operation.

It also forwards control information like data type, frame number, line number, virtual channel number and packet boundary signals, namely frame start, line start, line end and frame end.

### 3.3.6.7 MIPI Virtual Channel Interface

This is an optional interface. This module forwards the received pixel information to configured data channel. This module interfaces to eight pixel data channels. The decision on which data channel, the received pixel to be forwarded is controlled by the external ISP. The external ISP provides 8 set of control information (each set will have virtual channel and data type). This module along with pixel data also generates HYSNC and VSYNC signals for the respective virtual channel.

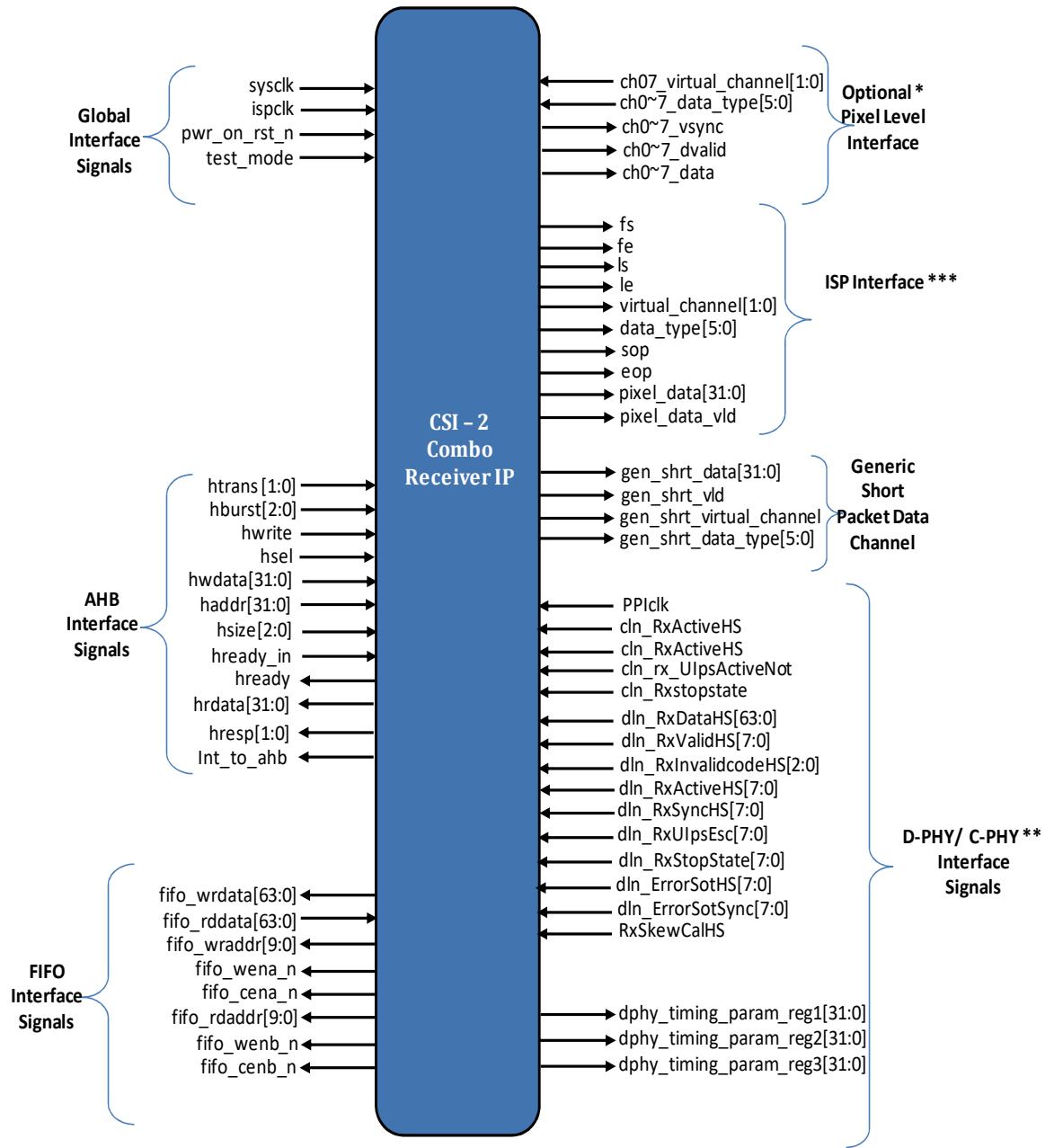

### 3.4 CSI-2 Combo Receiver Pin Diagram

Note:

- \* If the optional Pixel Interface is enabled, the other ISP interface is disabled.

- \*\*Based on configuration/PHY selected only fewer bits of the PPI signals are used.

- \*\*\*The pixel\_data and valid for the ISP shown is for one pixel mode, this will be increased for the multi pixel mode.

Figure 12: CSI-2 Receiver Combo PIN Diagram

## 3.5 SOC Level Integration

### 3.5.1 IP Deliverables

- Verilog HDL of the IP Core

- User guide

- Synthesis scripts

- Link report

- CDC report

- Verilog test suite

- Gate count estimates available upon request

### 3.5.2 Verification Environment

- Comprehensive suite of simulation tests for ease of SoC integration

- Verification components and test files provided

- Verification environment and test suite well documented

Figure 13: Verification Environment of CSI-2 Receiver IP

## 4 C-PHY + D-PHY Combo Physical Interface IP

### 4.1 Overview

The ever increasing demand for band width for the high resolution cameras resulted in to search for a simple, cost effective, rate efficient PHY which can support above 2.5Gbps. This search resulted into a new kind of PHY, which even at less channel rate provides very high data rate.

CPHY can achieve a very high data rate of 5.71Gbps per lane compared to the 2.5Gbps of DPHY1.2 or 1.5Gbps of DPHY1.1, still maintain the channel rate at 2.5Gsps which is same as DPHY1.2. CPHY achieves this by using a unique encoding mechanism in which 16 bit of input data is encoded into 7 symbols and each symbol is transmitted over a 3 Phase encoded line.

CPHY reuses the similar Low power signaling same as the DPHY. CPHY is designed such a way that it can co-exist sharing the same lines as DPHY. CPHY/DPHY combo IPs will be compatible to operate on the same channels used by DPHY, which offer a much wider area of application and flexibility. It can work with both old DPHY systems and is compatible with new CPHY.

Arasan's ComPHY is a CPHY/DPHY combo universal PHY which can be configured both as Transmitter and Receiver. Arasan's novel and innovative design techniques allowed sharing a number of modules between the CPHY and DPHY with no impact on performance resulting in optimal area and power.

### 4.2 C-PHY Based Interconnect Architecture

CPHY employs coding scheme in which clock can be recovered from the transmitted data. No separate clock lane is required in the interconnect and the slave will recover the clock from the data stream at the Slave side.

Each data lane is a 3 phase encoded requiring 3 separate line inter connections. Each lane interconnect provides up to 5.71 Gbps with effective data rate of 17.13 Gbps.

Figure 14: MIPI Link Diagram for CPHY

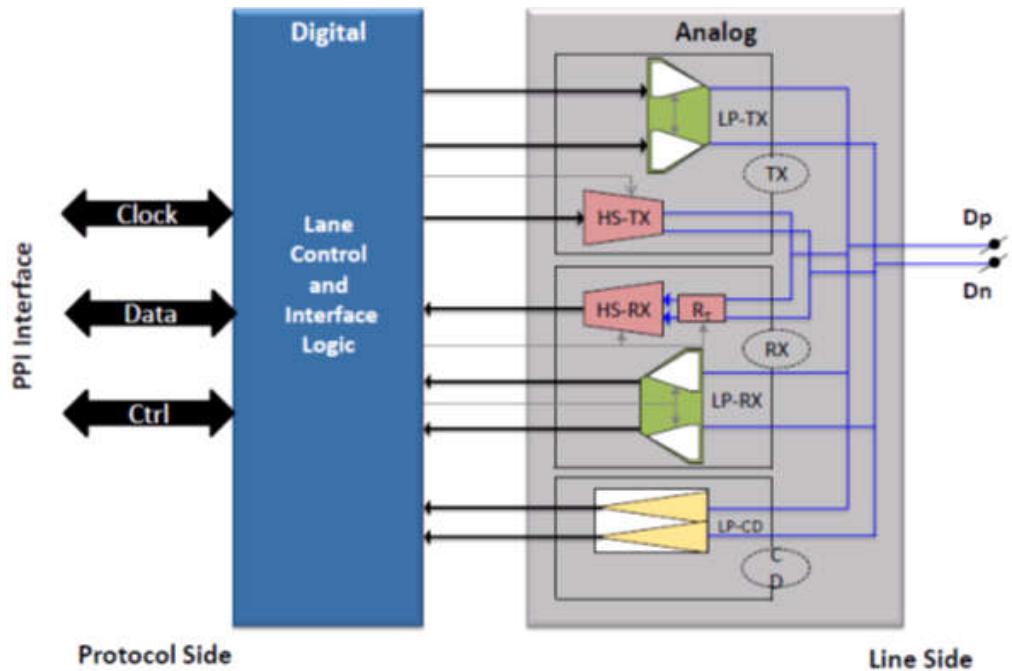

## 4.3 C-PHY Lane Architecture

Figure 15: C-PHY Lane Architecture

Each Lane Module has a control and interface logic unit and a transceiver portion to handle 3 Phase High-Speed functions, single-ended Low-Power functions operating on each of the interconnect wires individually. The I/O functions are controlled by the Lane Control and Interface Logic block.

High-Speed signals have a low voltage swing of 250 mV, while Low-Power signals have a large swing of 1.2V. High-Speed functions are used for High-Speed Data traffic. The Low-Power functions are mainly used for control and can have data transfer support.

High Speed data width is 16bit at the PPI side, which is converted to 7 Symbols by the mapper. Each symbol is 3 bits and it is encoded into a 3-phase signal by the encoder driver combination.

*Control and Interface Logic*, sends and detects start of packet signaling and end of packet signaling on the data lanes. It has a serializer and de-serializer unit to dialog with the PPI / PHY adapter unit. Also it has clock divider unit to source and receive data during parallel data transfers from and to the PPI.

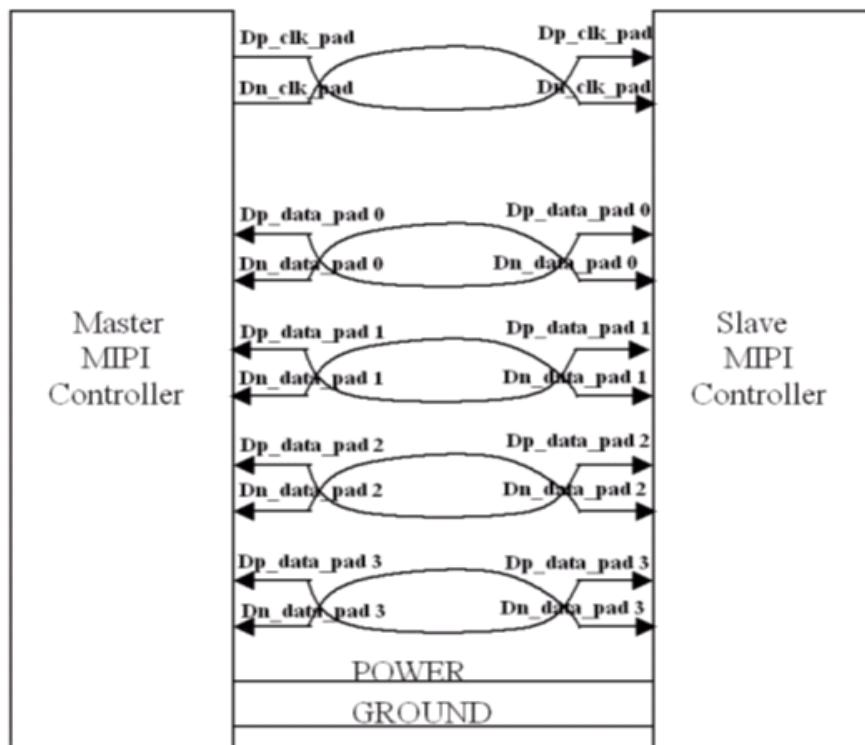

## 4.4 D-PHY Based Interconnect Architecture

DPHY employs a source synchronous scheme in which the High speed clock is transmitted using a separate channel along with the data lane. The clock maintains quadrature phase relationship to the data lane to ensure maximum margin between the clock and the data lane. Each data lane consists of two wires (Dp/Dn) and data is transmitted as differential signal on the both the edges of the clock.

Each lane interconnect provides up to 2.5 Gbps with effective data rate of 10 Gbps.

Figure 16: MIPI Link Diagram for DPHY

## 4.5 C-PHY – D-PHY Pad Table

Table 1: Functional description of D-PHY Pads for Clock Lane

| Pin<br>(D-PHY/<br>C-PHY) | Direction     | Description (D-PHY)                                                                     | Description (C-PHY)                   |

|--------------------------|---------------|-----------------------------------------------------------------------------------------|---------------------------------------|

| dpck /<br>lane1_A        | Bidirectional | Positive polarity of low voltage differential clock signal for transmitter and receiver | Wire A in the 3 wire lane of 1st lane |

| dnck /<br>lane1_B        | Bidirectional | Negative polarity of low voltage differential clock signal for transmitter and receiver | Wire B in the 3 wire lane of 1st lane |

| dp2 / lane1_C            | Bidirectional | Positive polarity of low voltage differential data signal for lane2                     | Wire C in the 3 wire lane of 1st lane |

| dn2 / lane2_A            | Bidirectional | Negative polarity of low                                                                | Wire A in the 3 wire lane of 2nd      |

|               |               |                                                                     |                                       |

|---------------|---------------|---------------------------------------------------------------------|---------------------------------------|

|               |               | voltage differential data signal for lane2                          | lane                                  |

| dp3 / lane2_B | Bidirectional | Positive polarity of low voltage differential data signal for lane3 | Wire B in the 3 wire lane of 2nd lane |

| dn3 / lane2_C | Bidirectional | Negative polarity of low voltage differential data signal for lane3 | Wire C in the 3 wire lane of 2nd lane |

| dp0 / lane0_A | Bidirectional | Positive polarity of low voltage differential data signal for lane0 | Wire A in the 3 wire lane of 1st lane |

| dn0 / lane0_B | Bidirectional | Negative polarity of low voltage differential data signal for lane0 | Wire B in the 3 wire lane of 1st lane |

| dp1 / lane0_C | Bidirectional | Positive polarity of low voltage differential data signal for lane1 | Wire C in the 3 wire lane of 1st lane |

| dn1           | Bidirectional | Negative polarity of low voltage differential data signal for lane1 |                                       |

Table 2: Power Pads

| Pins (DPHY/CPHY) | Direction | Description (DPHY)                         | Description (CPHY)            |

|------------------|-----------|--------------------------------------------|-------------------------------|

| VDD_clk          | Power     | Power pad for the clock lane               | Power pad for the data lane0  |

| VSS_clk          | Power     | Ground pad for the clock lane              | Ground pad for the data lane0 |

| VDD_d0d1         | Power     | Power pad for Data lane 0 and Data lane 1  | Power pad for the data lane1  |

| VSS_d0d1         | Power     | Ground pad for Data lane 0 and Data lane 1 | Ground pad for the data lane1 |

| VDD_d2d3         | Power     | Power pad for Data lane 2 and Data lane 3  | Power pad for the data lane2  |

| VSS_d2d3         | Power     | Ground pad for Data lane 2 and Data lane 3 | Ground pad for the data lane2 |

| VDDD             | Power     | Power pad for the DFE                      | Power pad for the DFE         |

| VSSD             | Power     | Ground pad for the DFE                     | Ground pad for the DFE        |

| VDDLP12          | Power     | Power pad for low power block              | Power pad for low power block |

Table 3: Analog Function Trimming Inputs

| Pins<br>(DPHY/<br>CPHY) | Direction | Description (DPHY) | Description (CPHY) |

|-------------------------|-----------|--------------------|--------------------|

| trim_0[31:0]            | Input     | Trim bits for DPHY | Trim bits for CPHY |

| trim_1[31:0]            | Input     | Trim bits for DPHY | Trim bits for CPHY |

| trim_2[31:0]            | Input     | Trim bits for DPHY | Trim bits for CPHY |

| trim_3[31:0]            | Input     | Trim bits for DPHY | Trim bits for CPHY |

Table 4: Clock and Reset Inputs

| Pins<br>(DPHY/<br>CPHY)      | Direction | Description (DPHY)                                                                                                                                                                                                        | Description (CPHY)                                                                                                                                                                                                        |

|------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxClkEsc                     | Input     | Escape mode Transmit Clock.<br>This clock is directly used to generate escape sequences. The period of this clock determines the symbol time for low power signals.<br>This is also the input reference clock for the PLL | Escape mode Transmit Clock.<br>This clock is directly used to generate escape sequences. The period of this clock determines the symbol time for low power signals.<br>This is also the input reference clock for the PLL |

| enable                       | Input     | Active Low system reset to the module                                                                                                                                                                                     | Active Low system reset to the module                                                                                                                                                                                     |

| dln_bd_ForceRx<br>mode       | Input     | Force Lane Module Into Receive mode / Wait for Stop state.<br>This signal forces the state machine into RX mode.                                                                                                          | Force Lane Module Into Receive mode / Wait for Stop state.<br>This signal forces the state machine into RX mode.                                                                                                          |

| dln_ForceTxStop<br>mode[3:0] | Input     | Force Lane Module Into Transmit mode / Generate Stop state.<br>This signal forces STOP signal on the transmit lines                                                                                                       | Only the first three bits are used for the CPHY.<br>Force Lane Module Into Transmit mode / Generate Stop state.<br>This signal forces STOP signal on the transmit lines                                                   |

Table 5: Clock Lane High Speed PPI Interface Signals

| Pins<br>(DPHY/<br>CPHY)      | Direction | Description (DPHY)                                                                                                                                                                                                                                                                                                                                                                    | Description (CPHY)                                                                                                                                                                                                                        |

|------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cln_TxRequestHS              | Input     | High-Speed Transmit Request and Data Valid for clock lane.<br>For clock Lanes, this active high signal causes the lane module to begin transmitting a high-speed clock                                                                                                                                                                                                                | -                                                                                                                                                                                                                                         |

| cln_RxActiveHS               | Output    | Receiver Clock Active.<br>This asynchronous, active high signal indicates that a clock Lane is receiving a DDR clock signal                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                         |

| TxByteClkHS /<br>TxWordClkHS | Output    | High-Speed Transmit Byte Clock.<br>This is used to synchronize PPI signals in the High-Speed transmit clock domain. It is recommended that all transmitting Data Lane Modules share one transmitter's byte clock signal. The frequency of byte clock is exactly 1/8 the High-Speed bit rate<br><br>This is the txbyteclkhs to which all PPI interface is synchronous for transmitter. | High-Speed Transmit Word Clock.<br>This is used to synchronize PPI signals in the high-speed transmit clock domain. The same clock is shared by all lane modules. The frequency of TxWordClkHS is exactly 1/7 the high-speed symbol rate. |

| RxByteClkHS /<br>RxWordClkHS | Output    | High-Speed Receive Byte Clock.<br>This is used to synchronize signals in the High-Speed receive clock domain. The rxbyteclkhs is generated by dividing the received High-Speed DDR clock<br><br>This is the byte clock to which all PPI interface is synchronous for receiver                                                                                                         | High-Speed Receive Word Clock.<br>This is used to synchronize signals in the high-speed receive clock domain. The RxWordClkHS is generated by dividing the recovered high-speed clock.                                                    |

Table 6: Clock lane Escape PPI interface Signals

| Pins<br>(DPHY/<br>CPHY) | Direction | Description (DPHY)                                                                                                                                                                                                                                                                                                                                                                    | Description (CPHY) |

|-------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| cIn_TxUlpsExit          | Input     | <p>Transmit ULP Exit Sequence for clock lane.</p> <p>This active high signal is asserted when ULP state is active and the protocol is ready to leave ULP state. The PHY leaves ULP state and begins driving Mark-1 when tx_ulpsactivenot_clk_n becomes deasserted.</p> <p>txulpsexit_clk is synchronous to txclkesc. This signal is ignored when the Lane is not in the ULP State</p> | -                  |

| cIn_TxUlpsClk           | Input     | To force the clock lane to transmit ULPS sequences in the clock line                                                                                                                                                                                                                                                                                                                  | -                  |

| cIn_RxUlpsClkNot        | Output    | <p>Receive Ultra Low-Power mode on Clock Lane.</p> <p>This active low signal is asserted to indicate that the Clock Lane module has entered the Ultra Low-Power mode. The Lane module remains in this mode with RxUlpsClkNot asserted until a Stop state is detected on the Lane Interconnect</p>                                                                                     | -                  |

| cIn_tx_UlpsActive Not   | Output    | ULP State (not) Active for clock lane. This active low signal is asserted to indicate that the Lane is in ULP state.                                                                                                                                                                                                                                                                  | -                  |

| cIn_rx_UlpsActive Not   | Output    | ULP State (not) Active for clock lane. This active low signal is asserted to indicate that the Lane is in ULP state.                                                                                                                                                                                                                                                                  | -                  |

**Table 7: Clock lane PPI Control Signals**

| <b>Pins<br/>(DPHY/<br/>CPHY)</b> | <b>Direction</b> | <b>Description (DPHY)</b>                                                                                                                                                                                                                                         | <b>Description (CPHY)</b> |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| cln_Rxstopstate                  | Output           | <p>Lane is in Stop state for clock lane.</p> <p>This active high signal indicates that the lane module is currently in Stop state. This is valid for both receivers and transmitters. Note that this signal is asynchronous to any clock in the PPI interface</p> | -                         |

**Table 8: Data lane High Speed PPI Interface Signals**

| <b>Pins<br/>(DPHY/<br/>CPHY)</b> | <b>Direction</b> | <b>Description (DPHY)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>Description (CPHY)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dln_TxDataHS[47 :0]              | Input            | <p>High-Speed Transmit Data for data lane.</p> <p>High-speed data to be transmitted. Data is captured on rising edges of transmitted byte clock.</p> <p>First 32 bits are only used for DPHY</p>                                                                                                                                                                                                                                                                                            | <p>High-Speed Transmit Data for data lane.</p> <p>High-speed data to be transmitted. Data is captured on rising edges of TxWordClkHS.</p>                                                                                                                                                                                                                                                                                                                                                                                              |

| dln_TxRequestHS [3:0]            | Input            | <p>High-Speed Transmit Request and Data Valid for data lane.</p> <p>A low-to-high transition on dln_TxRequestHS causes the lane module to initiate a Start-of-Transmission sequence. A high-to-low transition on dln_TxRequestHS causes the lane module to initiate an End-of- Transmission sequence.</p> <p>For Data Lanes, this active high signal also indicates that the protocol is driving valid data on txdatahs_0 to be transmitted. The lane module accepts the data when both</p> | <p>Only first three bits are used for the CPHY</p> <p>High-Speed Transmit Request and Data Valid for data lane.</p> <p>A low-to-high transition on dln_TxRequestHS causes the lane module to initiate a Start-of-Transmission sequence. A high-to-low transition on dln_TxRequestHS causes the lane module to initiate an End-of- Transmission sequence.</p> <p>For Data Lanes, this active high signal also indicates that the protocol is driving valid data on dln_TxDataHS to be transmitted. The lane module accepts the data</p> |

| Pins<br>(DPHY/<br>CPHY) | Direction | Description (DPHY)                                                                                                                                                                                                                                                                                                                                         | Description (CPHY)                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |           | <p>dln_TxRequestHS and dln_TxReadyHS are active on the same rising TxByteClkHS clock edge. The protocol always provides valid transmit data when txdatahs_0 is active. Once asserted, dln_TxDataHS remains high until the data has been accepted, as indicated by dln_TxReadyHS.</p> <p>dln_TxRequestHS is only asserted while dln_TxRequestEsc is low</p> | <p>when both dln_TxRequestHS and dln_TxReadyHS are active on the same rising TxWordClkHS clock edge. The protocol always provides valid transmit data when txdatahs_0 is active. Once asserted, dln_TxDataHS remains high until the data has been accepted, as indicated by dln_TxReadyHS.</p> <p>dln_TxRequestHS is only asserted while dln_TxRequestEsc is low</p> |

| dln_TxReadyHS [3:0]     | OUTPUT    | <p>High-Speed Transmit Ready for data lane.</p> <p>This active high signal indicates that dln_TxDataHS is accepted by the lane module to be serially transmitted. dln_TxReadyHS is valid on rising edges of transmitted byte clock</p>                                                                                                                     | <p>High-Speed Transmit Ready for data lane. First three bits only used for CPHY</p> <p>This active high signal indicates that dln_TxDataHS is accepted by the lane module to be serially transmitted. dln_TxReadyHS is valid on rising edges of TxWordClkHS</p>                                                                                                      |

| dln_TxSendSync HS[2:0]  | Input     | -                                                                                                                                                                                                                                                                                                                                                          | <p>High Speed Command to Transmit Sync Word.</p> <p>This command signal has the same timing as TxDataHS[15:0] on the PPI, but when TxSendSyncHS is active on a given TxWordClkHS cycle then TxDataHS[15:0] is ignored for any Word Clock cycle where TxSendSyncHS is active.</p>                                                                                     |

| dln_RxDataHS[47 :0]     | OUTPUT    | <p>High-Speed Receive Data for data lane.</p> <p>The signal connected to dln_RxDataHS was received first. Data is transferred on rising edges of receiver byte clock</p> <p>Only first 31 bits are used for DPHY</p>                                                                                                                                       | <p>High-Speed Receive Data for data lane.</p> <p>The signal connected to dln_RxDataHS was received first. Data is transferred on rising edges of RxWordClkHS</p>                                                                                                                                                                                                     |

| Pins<br>(DPHY/<br>CPHY)      | Direction | Description (DPHY)                                                                                                                                                                   | Description (CPHY)                                                                                                                                                                                                                  |

|------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dln_RxValidHS[3:<br>0]       | OUTPUT    | High-Speed Receive Data Valid for data lane                                                                                                                                          | High-Speed Receive Data Valid for data lane.<br>Only first three bits are used for CPHY                                                                                                                                             |

| dln_RxInvalidCod<br>eHS[2:0] | Output    | -                                                                                                                                                                                    | High-Speed Invalid Code Word Detection.<br>A high-speed status signal that indicates the present word on RxDataHS[15:0] was produced by a group of seven symbols that were not a valid code word.                                   |

| dln_RxActiveHS[3:<br>0]      | OUTPUT    | High-Speed Reception Active for data lane.<br><br>This active high signal indicates that the lane module is actively receiving a high-speed transmission from the lane interconnect. | High-Speed Reception Active for data lane.<br><br>This active high signal indicates that the lane module is actively receiving a high-speed transmission from the lane interconnect.<br><br>Only first three bits are used for CPHY |

Table 9: Data lane Escape mode PPI Signals

| Pins<br>(DPHY/<br>CPHY)    | Direction | Description (DPHY)                                                                                                                                                                                                                             | Description (CPHY)                                                                                                                                                                                                                                         |

|----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dln_TxRequestEs<br>c [3:0] | Input     | Escape mode Transmit Request for data lane.<br>dln_TxRequestEsc is only asserted by the protocol while dln_TxRequestHS is low.                                                                                                                 | Escape mode Transmit Request for data lane.<br>dln_TxRequestEsc is only asserted by the protocol while dln_TxRequestHS is low.<br>Only first three bits are used for the CPHY.                                                                             |

| dln_TxUlpsExit[3:<br>0]    | Input     | Transmit ULP Exit Sequence for data lane.<br><br>This active high signal is asserted when ULP state is active and the protocol is ready to leave ULP state. The PHY leaves ULP state and begins driving Mark- 1 when ulpsactivenot_0_n becomes | Transmit ULP Exit Sequence for data lane.<br><br>This active high signal is asserted when ULP state is active and the protocol is ready to leave ULP state. The PHY leaves ULP state and begins driving Mark- 1 when ulpsactivenot_0_n becomes deasserted. |

| Pins<br>(DPHY/<br>CPHY)  | Direction | Description (DPHY)                                                                                                                                                                                                                                                                                                                                       | Description (CPHY)                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |           | deasserted.<br>dln_TxUlpsExit is synchronous to TxClkEsc. This signal is ignored when the Lane is not in the ULP State.<br>Only first three bits are used for CPHY.                                                                                                                                                                                      | dln_TxUlpsExit is synchronous to TxClkEsc. This signal is ignored when the Lane is not in the ULP State.<br>Only first three bits are used for CPHY.                                                                                                                                                                                                                                                |

| dln_TxUlpsEsc[3:0]       | Input     | Escape mode Transmit Ultra Low Power for data lane.<br>This active high signal is asserted with dln_TxRequestEsc to cause the lane module to enter the ultra low power mode. The lane module remains in this mode until dln_TxRequestEsc is de-asserted.<br>dln_bd_TxLpdtEsc and all bits of dln_bd_TxTriggerEsc are low when dln_TxUlpsEsc is asserted. | Escape mode Transmit Ultra Low Power for data lane.<br>This active high signal is asserted with dln_TxRequestEsc to cause the lane module to enter the ultra low power mode. The lane module remains in this mode until dln_TxRequestEsc is de-asserted.<br>dln_bd_TxLpdtEsc and all bits of dln_bd_TxTriggerEsc are low when dln_TxUlpsEsc is asserted.<br>Only first three bits are used for CPHY |

| dln_bd_TxLpdtEsc         | Input     | This signal is used to request a low power data transmission entry in the forward direction.                                                                                                                                                                                                                                                             | This signal is used to request a low power data transmission entry in the forward direction.                                                                                                                                                                                                                                                                                                        |

| dln_bd_TxTriggerEsc[3:0] | Input     | A 4 bit signal that triggers a trigger sequence in the ESC mode in the forward direction                                                                                                                                                                                                                                                                 | A 4 bit signal that triggers a trigger sequence in the ESC mode in the forward direction                                                                                                                                                                                                                                                                                                            |

| dln_bd_TxDataEsc[7:0]    | Input     | In data mode, the 8-bit data to be transmitted in the forward direction.                                                                                                                                                                                                                                                                                 | In data mode, the 8-bit data to be transmitted in the forward direction.                                                                                                                                                                                                                                                                                                                            |

| dln_bd_TxValidEsc        | Input     | A valid signal which qualifies for the data lines.                                                                                                                                                                                                                                                                                                       | A valid signal which qualifies for the data lines.                                                                                                                                                                                                                                                                                                                                                  |

| dln_bd_TurnDisable       | Input     | To avoid the turn around request during the lock up situation                                                                                                                                                                                                                                                                                            | To avoid the turn around request during the lock up situation                                                                                                                                                                                                                                                                                                                                       |

| dln_bd_Direction         | Output    | To indicate the direction of the data lane.<br>This signal is used to indicate the current direction of the lane interconnect. When direction_0 =0, the lane is in transmit mode (0=Output). When direction_0 =1, the lane is in receive mode (1=Input)                                                                                                  | To indicate the direction of the data lane.<br>This signal is used to indicate the current direction of the lane interconnect. When direction_0 =0, the lane is in transmit mode (0=Output). When direction_0 =1, the lane is in receive mode (1=Input)                                                                                                                                             |

| Pins<br>(DPHY/<br>CPHY)  | Direction | Description (DPHY)                                                                                                                                                                                                                                                                                                       | Description (CPHY)                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dln_bd_TurnReq<br>uest   | Input     | This signal is used to request a Turn around operation for a bi-directional lane                                                                                                                                                                                                                                         | This signal is used to request a Turn around operation for a bi-directional lane                                                                                                                                                                                                                                                                                      |