# DATASHEET

# Universal Asynchronous Receiver/Transmitter (UART) Controller

Arasan Chip Systems, Inc. 2010 North First Street, Suite #510 San Jose, CA 95131 Ph:408-282-1600 Fx:408-282-7800 www.arasan.com

June, 2018

### DISCLAIMER

This document is written in good faith with the intent to assist the readers in the use of the product. Circuit diagrams and other information relating to Arasan Chip Systems' products are included as a means of illustrating typical applications. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. Information contained in this document is subject to continuous improvements and developments.

Arasan Chip Systems' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Arasan Chip Systems Inc. will be fully at the risk of the customer.

Arasan Chip Systems Inc. disclaims and excludes any and all warranties, including without limitation any and all implied warranties of merchantability, fitness for a particular purpose, title, and infringement and the like, and any and all warranties arising from any course or dealing or usage of trade.

This document may not be copied, reproduced, or transmitted to others in any manner. Nor may any use of information in this document be made, except for the specific purposes for which it is transmitted to the recipient, without the prior written consent of Arasan Chip Systems, Inc. This specification is subject to change at anytime without notice. Arasan Chip Systems Inc. is not responsible for any errors contained herein.

In no event shall Arasan Chip Systems Inc. be liable for any direct, indirect, incidental, special, punitive, or consequential damages; or for lost of data, profits, savings or revenues of any kind; regardless of the form of action, whether based on contract; tort; negligence of Arasan Chip Systems or others; strict liability; breach of warranty; or otherwise; whether or not any remedy of buyers is held to have failed of its essential purpose, and whether or not Arasan Chip Systems Inc. has been advised of the possibility of such damages.

#### **Restricted Rights**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

#### **Copyright Notice**

No part of this specification may be reproduced in any form or means, without the prior written consent of Arasan Chip Systems, Inc.

#### Questions or comments may be directed to:

Arasan Chip Systems, Inc. 2010 North First Street Suite 510, San Jose, CA 95131. Ph: 408-282-1600 Fx: 408-282-7800 Email: sales@arasan.com http://www.arasan.com

## CONTENTS

| 1 INTRODUCTION               |

|------------------------------|

| 1.1 Overview                 |

| 1.2 Features                 |

| 2 ARCHITECTURE               |

| 2.1 Host Interface5          |

| 2.2 Baud Rate Generator      |

| 2.3 Transmitter              |

| 2.4 Receiver                 |

| 2.5 Registers                |

| 3 PIN DIAGRAM                |

| 4 SIGNAL INTERFACES          |

| 5 SoC LEVEL INTEGRATION 10   |

| 5.1 Verification Environment |

| 5.2 IP Deliverables          |

| 6 RELATED PRODUCTS 10        |

## TABLES

| Table 1: UART Bus Interface Signals | . 8 |

|-------------------------------------|-----|

| Table 2: AHB Interface Signals      | . 8 |

| Table 3: Transmit RAM Signals       | . 9 |

| Table 4: Receive RAM Signals        | . 9 |

### **FIGURES**

| Figure 1: UART IP Block Diagram         | . 5 |

|-----------------------------------------|-----|

| Figure 2: PIN Diagram                   | . 7 |

| Figure 3: UART Verification Environment | 10  |

# **1 INTRODUCTION**

The Arasan 16550D High Speed UART IP core is a16550-compliant Universal Asynchronous Receiver/Transmitter (UART) with FIFO or expanded FIFO. UART complies to the standard 16550D with FIFOs. The UART performs serial to parallel conversion of the data received from the external device and parallel to serial conversion of data received from the AHB bus Interface. It supports both character and FIFO modes. The complete status of the UART can be read from its registers

#### **1.1 Overview**

The UART performs serial to parallel conversion of data received from the serial interface, and parallel to serial conversion of data received from the CPU interface. Both character and FIFO modes are supported. Operation of the UART can be programmed by a host processor through the host interface. Writing to the Control register determines the operational mode of the UART. The transmitter and receiver at the serial interface perform parallel to serial and serial to parallel conversion of data. Baud rate clock and receiver reference clock are generated by the Baud Rate Generator.

Writing to the Divisor Latch Registers (DLL and DLM) controls the clock rate. The interrupt controller signals the host processor in the event of error conditions such as transmission errors or modem status changes.

Complete status of the UART can be accessed by the host processor at any time. The Status registers provide information such as the modem status, line condition, line break, overrun, parity error, and other conditions.

The 16550D High Speed UART IP core implements a UART on an ASIC, or FPGA. The core includes RTL code, test scripts and a test environment for full simulation verifications. The Arasan 16550D High Speed UART IP core has been widely used in different applications by major chip vendors.

#### **1.2 Features**

- Complies with UART 16550D specification

- Complies with SD\_PHS Specification Ver1.0

- Supports character mode, FIFO mode, and extended FIFO mode

- Maximum 255 bytes FIFO size

- Programmable baud rate generator

- Maximum baud rate up to 1Mb/s

- 5-, 6-, 7-, or 8-bit per character

- 1, 1.5, or 2 stop bits.

- Even, odd, or stick parity

- Interrupt controller

- Complete status reporting

# **2 ARCHITECTURE**

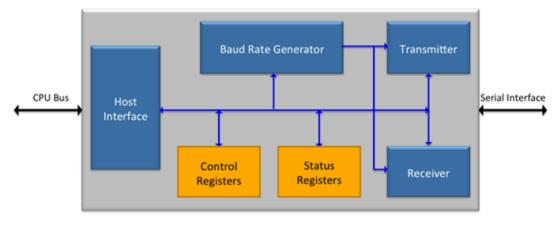

The architecture diagram of the UART IP is shown below.

Figure 1: UART IP Block Diagram

#### **2.1 Host Interface**

This block interfaces between the AHB bus master and UART. This merely acts as a AHB bus bridge. This works as a target module which functions according to the commands of AHB master model. It works in hclk. There are synchronizers for the control signals from the hclk to the UART clock.

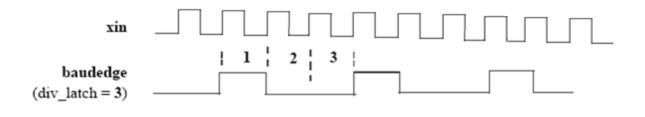

#### 2.2 Baud Rate Generator

The UART controller contains programmable baud generator that is capable of taking any clock input from DC to 24Mhz and dividing it by any divisor from 2 to 216-1. The output frequency of baud generator is 16 x the baud. This baud edge is used by transmit and receive blocks. Divisor latch value can be calculated by using the following formula Divisor = frequency input / (baud rate x 16)

This block converts the parallel data into serial data, adds the overhead bits and transmits through SOUT. The FIFO size for transmit is 256 bytes. An empty interrupt is generated when there is space for 16 bytes of data when extended FIFO enable bit is disabled. An empty interrupt is generated when there is space for 256 bytes of data when extended FIFO bit is enabled.

The three bit is set only when the FIFO is fully empty, that is when the last data is shifted to the transmit shift register (TSR). The TEMT bit is sent only when the stop bit of the last data has been fully transmitted. Number of stop bits, parity bit, and number of data bits can be controlled through the line control register. Data set ready and clear to send handshaking is checked in transmit block. Both FIFO mode and character mode are taken care.

#### 2.4 Receiver

This block receives the serial data and converts it into parallel data. FIFO size is 256 bytes. These trigger levels are programmed by the software through the FIFO control register. Framing error and brake interrupt error recovery is taken care in receiver. Parity checking and overrun error checking is handled. Each serial bit is sampled at the centre point. Time out interrupt is generated for both read and write timeouts. Both FIFO mode and character mode is taken care.

| Trigger level | Extended FIFO enable bit is'1' | FIFO enable<br>bit is '1' |

|---------------|--------------------------------|---------------------------|

| 2'b00         | 32                             | 1                         |

| 2'b01         | 64                             | 4                         |

| 2'b10         | 128                            | 8                         |

| 2'b11         | 192                            | 14                        |

#### **2.5 Registers**

This block decodes the address from the AHB bus to control all the UART Registers. All UART register's read and write takes place in this module. This also takes care of all read only, write only and read/write registers.

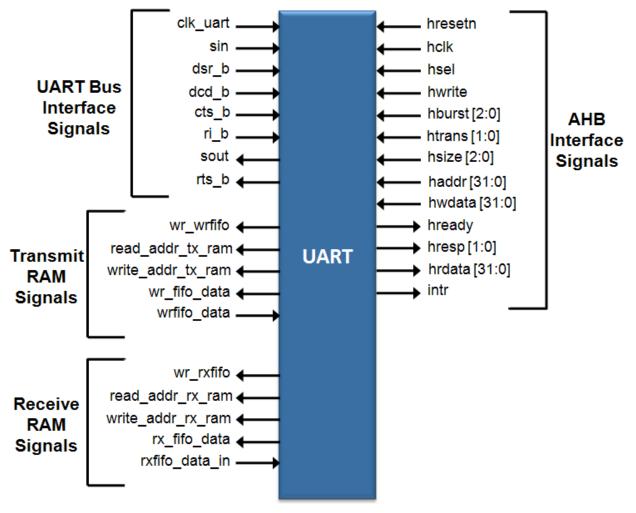

## **3 PIN DIAGRAM**

Figure 2: PIN Diagram

# arasan 4 SIGNAL INTERFACES

The signal names and its descriptions used in ARASAN AHB\_UART IP

- UART bus interface signals

- AHB bus interface signals

- Transmit RAM signals

- Receive RAM signals

#### Table 1: UART Bus Interface Signals

| Pin Name | Direction | Description                                                                                                                        | Power Up<br>Value |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| clk_uart | Input     | UART clock                                                                                                                         | Low               |

| sin      | Input     | Serial data input from MODEM                                                                                                       | High              |

| dsr_b    | Input     | Data set ready signal. Active low. RS232<br>interface pin when low indicates that the<br>MODEM is ready to establish communication | High              |

| dcd_b    | Input     | Active low data carrier detect signal from<br>MODEM                                                                                | High              |

| cts_b    | Input     | Active low clear to send signal from MODEM                                                                                         | High              |

| ri_b     | Input     | Active low ring indicator signal from MODEM                                                                                        | High              |

| sout     | Output    | Serial data output to MODEM                                                                                                        | High              |

| rts_b    | Output    | Active low request to send signal to MODEM                                                                                         | High              |

#### Table 2: AHB Interface Signals

| Pin Name    | Direction | Description                                                                                                                                                         | Power Up<br>Value |

|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| hresetn     | Input     | Active low reset                                                                                                                                                    | Low               |

| hclk        | Input     | AHB processor clock. All signal timings are related to the rising edge of hclk                                                                                      | Low               |

| hsel        | Input     | Slave select signal                                                                                                                                                 | High              |

| hwrite      | Input     | When high, this signal indicates a write transfer and when low a read transfer                                                                                      | Low               |

| hburst[2:0] | Input     | Indicates if the transfer forms the part of the<br>burst. Four eight and sixteen beat bursts are<br>supported. The burst may be either<br>incrementing and wrapping | Low               |

| htrans[1:0] | Input     | Indicates the type of current transfer which can be non sequential, sequential, idle or busy                                                                        | Low               |

| hsize[2:0]  | Input     | Indicates the size of the transfer which is typically byte, half word or word                                                                                       | Low               |

| Pin Name     | Direction | Description                                                                                                            | Power Up<br>Value |

|--------------|-----------|------------------------------------------------------------------------------------------------------------------------|-------------------|

| haddr[31:0]  | Input     | The 32 bit system address. This signal is routed to the AHB target core                                                | Low               |

| hwdata[31:0] | Input     | The write data bus is used to transfer data from master to the bus slave during write operation                        | Low               |

| hready       | Output    | When high this signal indicates the transfer has finished on the bus. This signal is driven low to extend the transfer | High              |

| hresp[1:0]   | Output    | The transfer response provides additional information on the status of the transfer, OKAY, ERROR, RETRY or SPLIT       | Low               |

| hrdata[31:0] | Output    | The read data bus is used to transfer the data from bus slave to the bus master                                        | Low               |

| intr         | Output    | Interrupt                                                                                                              | Low               |

#### Table 3: Transmit RAM Signals

| Pin Name          | Direction | Description                         | Power Up<br>Value |

|-------------------|-----------|-------------------------------------|-------------------|

| wr_wrfifo         | Output    | Write enable signal to transmit RAM | Low               |

| read_addr_tx_ram  | Output    | Read address to transmit RAM        | Low               |

| write_addr_tx_ram | Output    | Write address to transmit RAM       | Low               |

| wr_fifo_data      | Output    | Write data to transmit RAM          | Low               |

| wrfifo_data       | Input     | Read data from Transmit RAM         | Low               |

#### Table 4: Receive RAM Signals

| Pin Name          | Direction | Description                        | Power Up<br>Value |

|-------------------|-----------|------------------------------------|-------------------|

| wr_rxfifo         | Output    | Write enable signal to receive RAM | Low               |

| read_addr_rx_ram  | Output    | Read address to receive RAM        | Low               |

| write_addr_rx_ram | Output    | Write address to receive RAM       | Low               |

| rx_fifo_data      | Output    | Write data to receive RAM          | Low               |

| rxfifo_data_in    | Input     | read data from receive RAM         | Low               |

# arasan 5 SoC LEVEL INTEGRATION

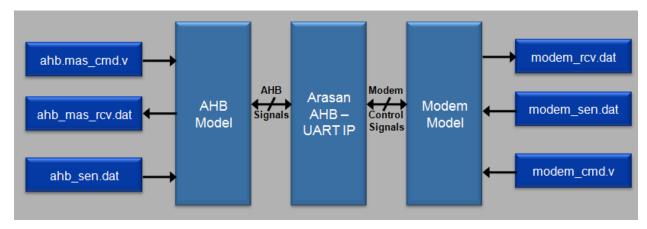

#### **5.1 Verification Environment**

This section displays the UART RTL verification and test environment.

**Figure 3: UART Verification Environment**

## **5.2 IP Deliverables**

The IP package consists of the following:

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

# **6 RELATED PRODUCTS**

- I2S Controller

- I2C Controller

- SPI