# Datasheet

**USB 2.0 Total IP Solution**

# Arasan Chip Systems Inc.

2010 North First Street, Suite #510, San Jose, CA 95131

Ph: 408-282-1600 Fax: 408-282-7800 www.arasan.com

#### Disclaimer

This document is written in good faith with the intent to assist the readers in the use of the product. Circuit diagrams and other information relating to Arasan Chip Systems' products are included as a means of illustrating typical applications. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. Information contained in this document is subject to continuous improvement and development.

Arasan Chip Systems' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Arasan Chip Systems Inc. will be fully at the risk of the customer.

Arasan Chip Systems Inc. disclaims and excludes any and all warranties, including, without limitation, any and all implied warranties of merchantability, fitness for a particular purpose, title, and infringement and the like, and any and all warranties arising from any course or dealing or usage of trade.

This document may not be copied, reproduced, or transmitted to others in any manner. Nor may any use of information in this document be made, except for the specific purposes for which it is transmitted to the recipient, without the prior written consent of Arasan Chip Systems Inc. This specification is subject to change at any time without notice. Arasan Chip Systems Inc. is not responsible for any errors contained herein.

In no event shall Arasan Chip Systems Inc. be liable for any direct, indirect, incidental, special, punitive, or consequential damages; or for loss of data, profits, savings or revenues of any kind; regardless of the form of action, whether based on contract; tort; negligence of Arasan Chip Systems Inc or others; strict liability; breach of warranty; or otherwise; whether or not any remedy of buyers is held to have failed of its essential purpose, and whether or not Arasan Chip Systems Inc. has been advised of the possibility of such damages.

#### **Restricted Rights**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

#### **Copyright Notice**

No part of this specification may be reproduced in any form or means, without the prior written consent of Arasan Chip Systems, Inc.

Questions or comments may be directed to:

Arasan Chip Systems Inc. 2010 North First Street, Suite 510 San Jose, CA 95131

Ph: 408-282-1600 Fax: 408-282-7800

Email: sales@arasan.com

# Contents

| 1 | Int          | roduction                              | . 1 |

|---|--------------|----------------------------------------|-----|

|   | 1.1          | Arasan's Contribution to USB           | 1   |

|   | 1.2          | Arasan's Total IP Solution             |     |

| 2 | USI          | B 2.0 Host IP                          | . 3 |

|   |              |                                        |     |

|   | 2.1          | Overview                               |     |

|   | 2.2          | Features                               |     |

|   | 2.3          | Architecture                           |     |

|   | 2.3.<br>2.3. |                                        |     |

|   | 2.3.         | PIN Diagram                            |     |

|   | 2.5          | Signal Interfaces                      |     |

|   | 2.6          | SoC Level Integration                  |     |

|   | 2.6.         | 5                                      |     |

|   | 2.6.         |                                        |     |

| _ |              |                                        |     |

| 3 | USI          | B 2.0 Hub IP                           | 12  |

|   | 3.1          | Overview                               | 12  |

|   | 3.2          | Features                               | 12  |

|   | 3.3          | Architecture                           | 14  |

|   | 3.3.         | 1 Functional Block Diagram             | .14 |

|   | 3.3.         | 2 Functional Block Diagram Description | .14 |

|   | 3.4          | Signal Interfaces                      | 16  |

|   | 3.5          | SoC Level Integration                  | 21  |

|   | 3.5.         |                                        |     |

|   | 3.5.         | 2 IP Deliverables                      | .21 |

| 4 | USI          | B 2.0 Device IP                        | 22  |

|   | 4.1          | Overview                               | 22  |

|   | 4.2          | Features                               |     |

|   | 4.3          | Architecture                           |     |

|   | 4.3.         |                                        |     |

|   | 4.3.         | •                                      |     |

|   | 4.4          | Pin Details                            |     |

|   | 4.5          | Signal Interfaces                      | 25  |

|   | 4.5.         |                                        |     |

|   | 4.6          | SoC Level Integration                  | 29  |

|   | 4.6.         | 1 Verification Environment             | .29 |

|   | 4.6.         | 2 IP Deliverables                      | .29 |

| 5 | USB 2   | 2.0 OTG IP                           | 30 |

|---|---------|--------------------------------------|----|

|   | 5.1 O   | verview                              | 30 |

|   | 5.2 Fe  | eatures                              | 30 |

|   | 5.3 Ar  | chitecture                           | 31 |

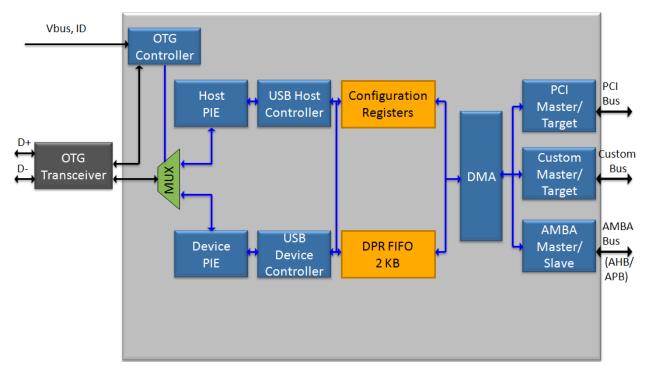

|   | 5.3.1   | Functional Block Diagram             | 31 |

|   | 5.3.2   | Functional Block Diagram Description | 32 |

|   | 5.4 Sig | gnal Interfaces                      | 34 |

|   | 5.5 Sc  | C Level Integration                  | 38 |

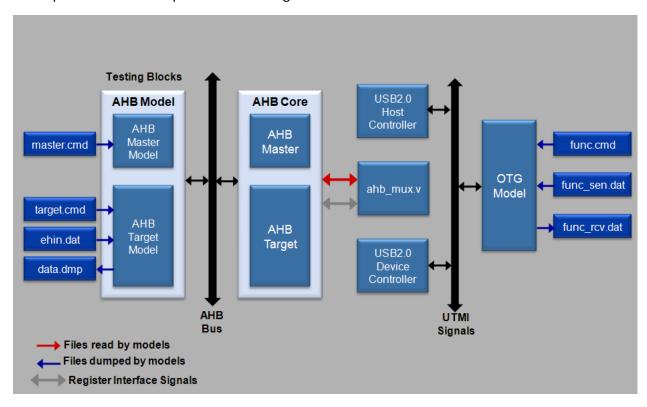

|   | 5.5.1   | Verification Environment             | 38 |

|   | 5.5.2   | IP Deliverables                      | 38 |

| 6 | USB 2   | 2.0 PHY IP                           | 39 |

|   | 6.1 Ov  | verview                              | 39 |

|   | 6.2 Fe  | eatures                              | 39 |

|   | 6.3 Ar  | chitecture                           | 40 |

|   | 6.3.1   | System on Chip Description           | 40 |

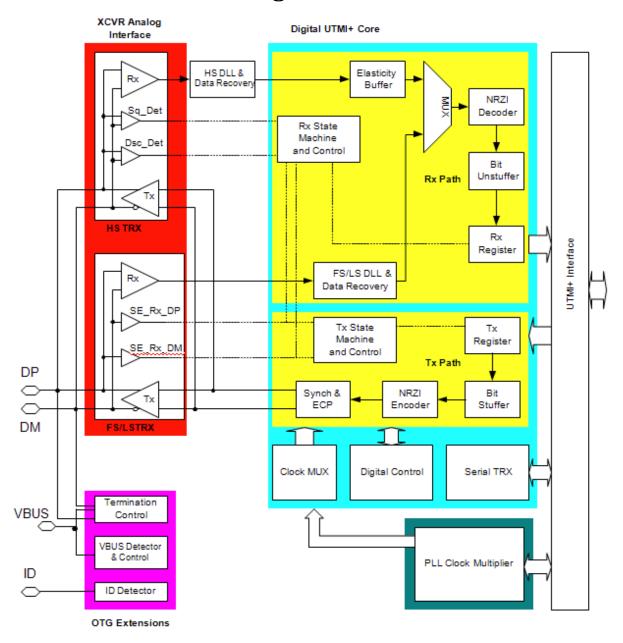

|   | 6.4 Fu  | unctional Block Diagram              | 41 |

|   | 6.4.1   | Functional Block Description         | 42 |

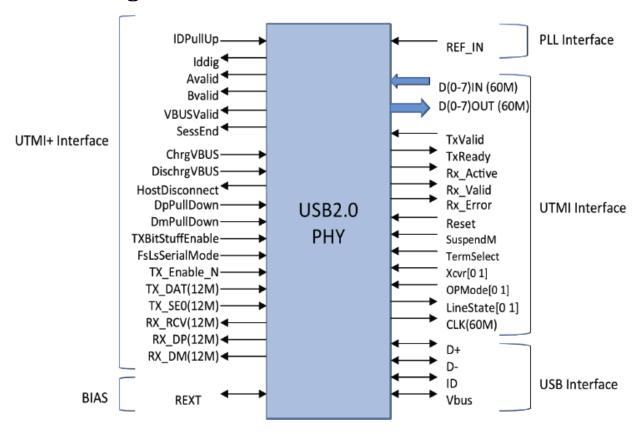

|   | 6.5 Pi  | n Diagram                            | 46 |

|   | 6.5.1   | Pin Description                      | 46 |

|   | 6.6 Sc  | oC Level Integration                 | 48 |

|   | 6.6.1   | Verification Environment             | 48 |

|   | 6.6.2   | IP Deliverables                      | 48 |

| 7 | USB 2   | 2.0 HSIC PHY IP                      | 49 |

|   | 7.1 O   | verview                              | 49 |

|   | 7.2 Fe  | eatures                              | 49 |

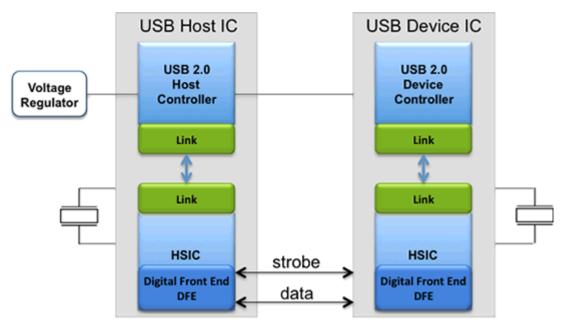

|   | 7.3 Ar  | chitecture                           | 49 |

|   | 7.3.1   | Functional Description               | 49 |

|   | 7.3.2   | Functional Block Diagram             |    |

|   | 7.3.3   | Functional Block Diagram Description | 50 |

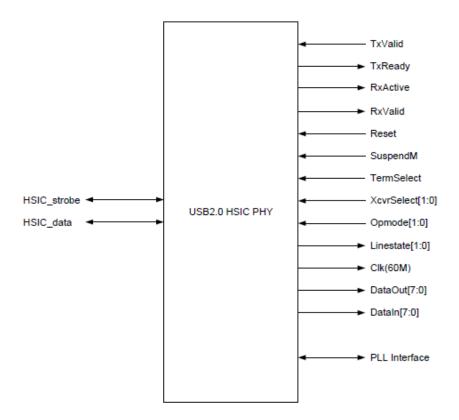

|   | 7.4 Pi  | n Diagram                            | 51 |

|   | 7.5 Sc  | oC Integration                       | 52 |

|   | 7.5.1   | Verification Environment             | 52 |

|   | 7.5.2   | IP Deliverables                      | 52 |

| 8 | Servi   | ces & Support                        | 53 |

|   | 8.1 GI  | obal Support                         | 53 |

|   |         | asan Support Team                    |    |

|   |         | ofessional Services & Customization  |    |

|   |         | ne Arasan Porting Engine             |    |

|   |         |                                      |    |

| 8.5      | Pricing & Licensing                              | 53 |

|----------|--------------------------------------------------|----|

| Tabl     | es                                               |    |

| Table 1  | L: EHCI DMA Interface Signals                    | 8  |

|          | 2: OHCI DMA Interface Signals                    |    |

|          | 3: HUB2.0 Upstream Port PIN Description          |    |

|          | 1: HUB2.0 Downstream Port PIN Description        |    |

|          | 5: UTMI+ Interface Signals                       |    |

|          | 5: AHB Interface Signals                         |    |

| Table 7  | 7: Bus Interface Signals                         | 34 |

| Table 8  | 3: AHB Bus Interface Signals                     | 36 |

| Table 9  | 9: Pin Description                               | 46 |

|          |                                                  |    |

| Figu     | res                                              |    |

| Figure : | 1: Arasan's Total IP Solution                    | 2  |

| Figure 2 | 2: USB Host IP Core Functional Block Diagram     | 4  |

| Figure 3 | 3: USB Host IP Pinout Diagram                    | 7  |

| _        | 4: Verification Environment                      |    |

| Figure ! | 5: USB 2.0 HUB IP Core Functional Block Diagram  | 14 |

|          | 6: RTL Verification Environment                  |    |

| Figure : | 7: USB 2.0 Device IP Core Block Diagram          | 23 |

| Figure 8 | 8: Pinout Diagram                                | 25 |

| Figure 9 | 9: USB 2.0 Verification Environment              | 29 |

| Figure : | 10: USB 2.0 OTG IP Core Functional Block Diagram | 31 |

| Figure : | 11: OTG Testing Environment                      | 38 |

| Figure : | 12: System on Chip Block Diagram                 | 40 |

| Figure : | 13: Functional Block Diagram                     | 41 |

| Figure : | 14: Pin Diagram                                  | 46 |

| Figure : | 15: USB 2.0 HSIC PHY Functional Block Diagram    | 50 |

| Figure : | 16: USB 2.0 HSIC PHY PIN Diagram                 | 51 |

# 1 Introduction

Universal Serial Bus (USB) is an industry standard that defines the cables, connectors and communications protocols used in a bus for connection, communication, and power supply between computers and electronic devices. USB standardizes the connection of computer peripherals (including keyboards, pointing devices, digital cameras, printers, portable media players, disk drives and network adapters) to personal computers, both to communicate and to supply electric power. It has become commonplace on other devices, such as smartphones, PDAs and video game consoles.

# 1.1 Arasan's Contribution to USB

Arasan Chip Systems provides a complete suite of USB-compliant IP including low speed, high speed and super speed USB products. Arasan became a member if the USB-IF standards body in 1996 and delivered its first USB 1.0 IP product in that year. The offering expanded to USB 2.0 products in 2000 and USB 3.0 products in 2009. Arasan's customer base includes many major systems and SoC companies in variety of industries.

Arasan is the only company to offer a USB Total IP Solution. In addition to offering a complete suite of digital IP for USB, Arasan's analog IP team onlhas also developed the USB 2.0 PHY and USB HSIC PHY. As part of its end-to-end solution approach to IP, Arasan also offers USB 3.0 software stacks and drivers which are backward compatible with 2.0 specifications.

Arasan's active involvement and contribution to the relevant standards bodies, lead to deep domain expertise, which in turn results in early availability of high quality standards compliant IP for our customers.

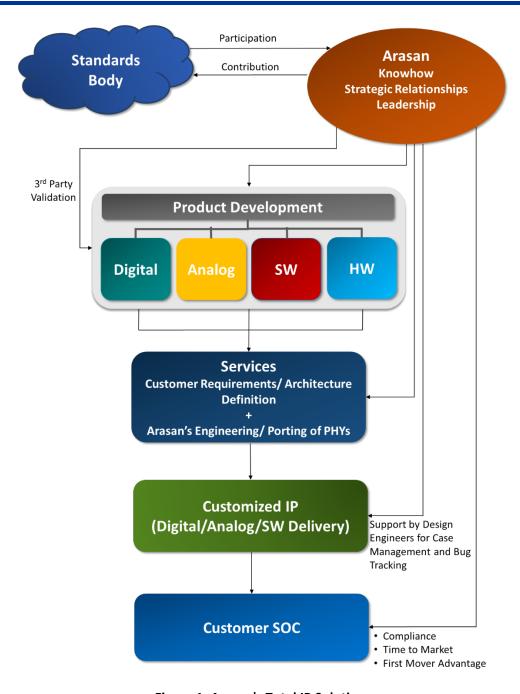

# 1.2 Arasan's Total IP Solution

Arasan provides a Total IP Solution, which encompasses all aspects of IP development and integration, including analog and digital IP cores, verification IP, software stacks & drivers, and hardware validation platforms. Benefits of Total IP Solution:

- Seamless integration from PHY to Software

- Assured compliance across all components

- Single point of support

- Easiest acquisition process (one licensing source)

- Lowest overall cost including cost of integration

- Lowest risk for fast time to market

Figure 1: Arasan's Total IP Solution

# 2 USB 2.0 Host IP

### 2.1 Overview

The Arasan USB 2.0 Host IP is an USB 2.0 specification compliant host IP core with an optional AHB, PCI, or custom host interface. The USB 2.0 Host IP supports

- 480 Mbit/s in High Speed (HS) mode

- 12 Mbit/s in Full Speed (FS) mode

- 1.5 Mbit/s in Low Speed (LS) mode

The Arasan's USB 2.0 Host controller is designed for flexibility and ease of use and facilitates implementation of a wide variety of applications with fast turnaround time. This design is technology independent and migrating to any technology is fast and simple. This EHC can be easily interfaced to standard buses such as ARM, S-Bus and so on.

The IP consists of an Enhanced Host Controller Interface (EHCI) and a companion Open Host Controller Interface (OHCI). The EHCI processor handles HS transactions and is the default owner of the root hub that connects to the downstream ports. In a downstream data transfer, the EHCI sends data to the Host Parallel Interface Engine (HPIE) for encoding and CRC appending. Data received by the USB 2.0 Root Hub is forwarded to the downstream ports. Similarly, FS and LS transactions are handled by the OHCI, Host Serial Interface Engine (HSIE), and USB 1.1 Root Hub.

The Root Hub performs multiplexing and forwarding of packets between the downstream ports and USB 2.0/1.1 Root Hubs. Up to 8 downstream ports can be connected to the USB 2.0 Host IP core. With the addition of an optional ULPI Wrappers, the Arasan USB 2.0 Host IP core can be connected directly to a 16-bit standard UTMI+ or 8-bit ULPI transceiver.

# 2.2 Features

- Compliant with the following specification versions:

- USB specification revision 2.0 EHCl specification revision 1.0

- USB 2.0 Host:

- Supports up to 127 devices and 8 downstream ports

- OHCI companion processor for USB 1.1 transfers

- 16-bit UTMI+ and 8-bit ULPI interfaces

- Direct addressing all IP core registers from AHB, PCI, or custom bus

- DMA controller supports high-speed data transfers between USB Host IP and host bus

- Supports low, full and high speed devices

- Technology independent

- Integrated root hub with up to 3 ports

- Host Interface:

- 8, 16, or 32-bit host bus

- Optional 133 MHz AHB Rev. 2.0 master/slave interface

- Optional 33 MHz PCI Rev. 2.2 master/target interface

- Optional custom bus interface

# 2.3 Architecture

### 2.3.1 Functional Block Diagram

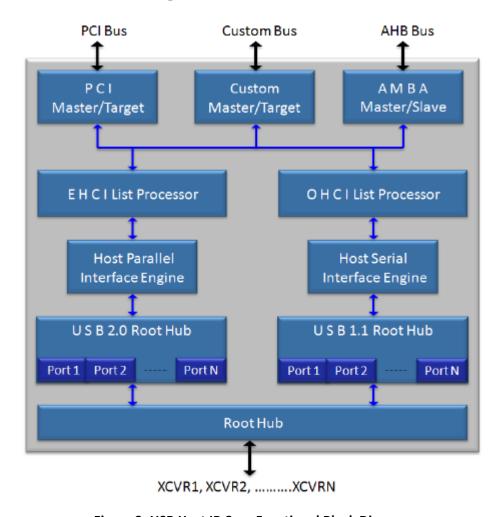

Figure 2: USB Host IP Core Functional Block Diagram

### 2.3.2 Functional Block Diagram Description

#### 2.3.2.1 PCI Master/Slave Function

The PCI Master/Slave function is a bus interface unit that performs all data transfers necessary for the back-end core to access the system memory as well as the data transfers necessary for the bus master to access the PCI BUS. The target functionality supports memory read/write and configuration read/write commands. It has two functions. Function zero corresponds to USB 1.1 Host controller and Function two to USB 2.0 Host controller. The master supports memory read and memory write burst and single data phase transactions. The main functions are reading and writing EHCI specific data structures and data transfer from the system memory to the device and viceversa. An optional PCI version 2.2 master/target interfaces allows a PCI host to access all registers in the USB 2.0 Host IP. The PCI interface supports programmable I/O and DMA data transfer methods. In programmable I/O method, the PCI host driver transfers data using the Buffer Data Port register. In DMA method, the DMA controller is the bus master during the data transfer. The PCI master/target interface also supports Power management conforming to the PCI power management interface specification.

#### 2.3.2.2 Custom Interface (Optional)

Custom bus with special requirements such as a bus width from 4-bit to 64-bit can be provided by Arasan Chip Systems. The custom bus can be used to support processors such as 8051. A DMA controller can also be included as an optional module. Host processor connected to the custom bus has direct access to all registers in the USB 2.0 Host IP. Configuration and operation of the USB host core can be controlled by the host processor.

### 2.3.2.3 AHB Interface (Optional)

The AHB master/slave interface provides a high-speed connection between the AHB host and USB 2.0 host controller. When operating as an AHB slave, the DMA controller can be used to manage the high-speed data transfers. The AHB host has direct access to all registers in the USB 2.0 Host IP. Configuration and operations of the USB host can be controlled by an AHB host through the AHB interface.

#### 2.3.2.4 UTMI+ Interface

The Arasan USB 2.0 Host IP core implements a 16-bit UTMI+ compliant module that provides a seamless interface to standard interface components such as the Philips USB 2.0 UTMI+ transceiver.

#### 2.3.2.5 ULPI Interface

The Arasan USB 2.0 Host IP core provides an optional UTMI+ to ULPI wrapper. Instead of using a high pin count UTMI+ interface, user may choose to use an ULPI interface to reduce the pin count to 12.

#### 2.3.2.6 EHCI List Processor

This block takes care of the USB transaction with high speed devices, which are USB 2.0 compliant. It processes the EHCI version 2.0 specific data structures.

#### 2.3.2.7 OHCI List Processor

This block takes care of the USB transaction with full and low speed devices, which are specification 1.1 compliant. This block only processes USB 1.1 compliant data structures.

### 2.3.2.8 Host Parallel Interface Engine (HPIE)

This parallel interface engine decodes the packet from the device and also does CRC checking Supports 127 devices bridging the core to other system buses like ARM, Motorola, and Sun and so on. Supports Control, Bulk, and Isochronous and interrupt data transfer types.

#### 2.3.2.9 Host Serial Interface Engine (HSIE)

This is the host serial interface engine for USB1.1 OHCI List processor engine. It does NRZI encoding / decoding, bitstuffing / debitstuffing, CRC checking / generation, packet decoding and serial to parallel conversions and vice-versa.

#### 2.3.2.10 USB 2.0 Root Hub

This block takes care of USB 2.0 device specific connect/disconnect, power management, suspend and resume signaling.

#### 2.3.2.11 USB 1.1 Root Hub

This block takes care of USB 1.1 device specific connect/disconnect, power management, suspend and resume signaling.

#### 2.3.2.12 Root Hub

Depending on device speed this block switches different downstream devices to either USB 2.0 or USB 1.1 root hubs.

# 2.4 PIN Diagram

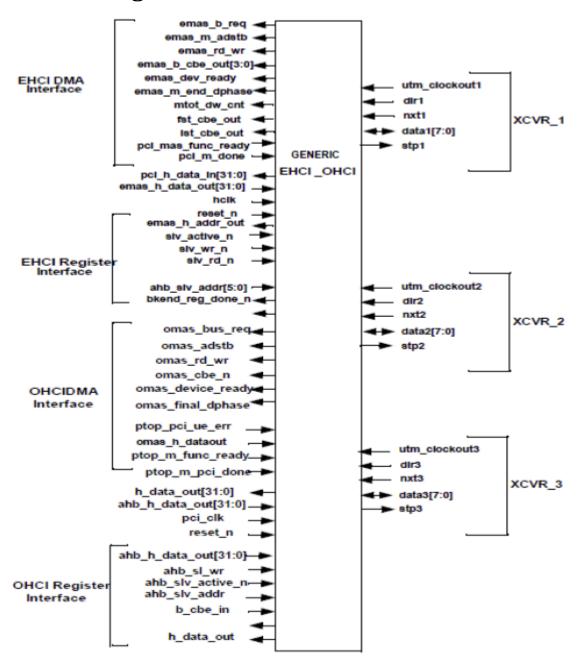

Figure 3: USB Host IP Pinout Diagram

# 2.5 Signal Interfaces

**Table 1: EHCI DMA Interface Signals**

| Pin                   | Direction | Description                                                             |

|-----------------------|-----------|-------------------------------------------------------------------------|

| data_in [31:0]        | OUT       | Register write data to EHCI                                             |

| data_out [31:0]       | IN        | Register read data from EHCI                                            |

| fst_cbe_out[3:0]      | OUT       | This pin indicates the first valid byte                                 |

| lst_cbe_out[3:0]      | OUT       | This pin indicates the last valid byte                                  |

| emas_b_req            | OUT       | EHCI request to system master core to perform DMA                       |

| em_m_adstb            | OUT       | EHCI indicates the presence of DMA address on data lines                |

| emas_rd_wr            | OUT       | Backend indicates to system master core to do a read or write operation |

|                       |           | 0 - Read. 1 - Write                                                     |

| emas_b_cbe_out [3:0]  | OUT       | EHCI provides byte enables for write transfer. Has                      |

| cinas_b_cbc_out [5.0] | 001       | same timing as write data                                               |

| emas_device_ready     | OUT       | EHCI indicates that it is ready for DMA transfer. It                    |

| emas_acvice_ready     |           | should not be deasserted before the DMA completes                       |

| emas_m_end_dphase     | OUT       | Asserted by EHCI for last beat                                          |

| pci_m_func_rdy        | OUT       | Asserted by the system core whenever there is a                         |

|                       |           | successful transfer                                                     |

| mtot_dword_cnt        | OUT       | Number of Dwords transferred                                            |

| fst_cbe_out           | OUT       | First valid byte                                                        |

| lst_cbe_out           | OUT       | Last valid byte                                                         |

| emas_h_dataout        | OUT       | Output data from EHCI                                                   |

| pci_h_data_in         | IN        | Input data to EHCI                                                      |

| pci_m_done            | OUT       | Asserted by the system core when the last byte for                      |

|                       |           | current DMA transfers                                                   |

| hclk                  | IN        | 133mhz clock frequency                                                  |

| hreset_n              | IN        | Active low reset signal                                                 |

| utm_clockout1         | IN        | Interface clock. 60 MHZ Input clock from ULPI PHY                       |

| dir1                  | IN        | Input signal from ULPI PHY, controls the direction of the               |

|                       |           | data bus. The PHY pulls dir high whenever the interface                 |

|                       |           | cannot accept data from the Link                                        |

| nxt1                  | IN        | Input signal from the PHY used to throttle all data types,              |

|                       |           | except register read data and the RX CMD. Identical to                  |

|                       |           | RX valid during USB receive, and TX Ready during USB                    |

|                       |           | transmit. The PHY also asserts nxt and dir                              |

|                       |           | simultaneously to indicate USB receive activity                         |

|                       |           | (RXActive), if dir was previously low. The PHY is not                   |

|                       |           | allowed to assert nxt during the first cycle of the TX CMD              |

|                       |           | driven by the Link                                                      |

| stp1                  | OUT       | Output to ULPI PHY. The Link must assert stp to signal                  |

|                       |           | the end of a USB transmit packet or a register write                    |

|                       |           | operation, and optionally to stop any receive. The step                 |

|                |       | signal must be asserted in the cycle after the last data   |

|----------------|-------|------------------------------------------------------------|

|                |       | byte is presented on the bus                               |

| data1[7:0]     | INOUT | 8 bit data bus. Driven to 00h by the Link when the ULPI    |

|                |       | bus is idle. The signals in this bus are synchronized with |

|                |       | positive edge of clk60                                     |

| utm_clockout2. | IN    | Interface clock. 60 MHZ Input clock from ULPI PHY          |

| dir2           | IN    | Input signal from ULPI PHY, controls the direction of the  |

|                |       | data bus. The PHY pulls dir high whenever the interface    |

|                |       | cannot accept data from the Link                           |

| nxt2           | IN    | Input signal from the PHY used to throttle all data types, |

|                |       | except register read data and the RX CMD. Identical to     |

|                |       | RX valid during USB receive, and TX Ready during USB       |

|                |       | transmit. The PHY also asserts nxt and dir                 |

|                |       | simultaneously to indicate USB receive activity (          |

|                |       | RXActive), if dir was previously low. The PHY is not       |

|                |       | allowed to assert nxt during the first cycle of the TX CMD |

|                |       | driven by the Link                                         |

| stp2           | OUT   | Output to ULPI PHY. The Link must assert stp to signal     |

|                |       | the end of a USB transmit packet or a register write       |

|                |       | operation, and optionally to stop any receive. The stp     |

|                |       | signal must be asserted in the cycle after the last data   |

|                |       | byte is presented on the bus                               |

| data2[7:0]     | INOUT | 8 bit data bus. Driven to 00h by the Link when the         |

|                |       | ULPI bus is idle. The signals in this bus are synchronized |

|                |       | with positive edge of clk60                                |

| utm_clockout3  | IN    | Interface clock. 60 MHZ Input clock from ULPI PHY          |

| dir3           | IN    | Input signal from ULPI PHY, controls the direction of the  |

|                |       | data bus. The PHY pulls dir high whenever the interface    |

| _              |       | cannot accept data from the Link                           |

| nxt3           | IN    | Input signal from the PHY used to throttle all data types, |

|                |       | except register read data and the RX CMD. Identical to     |

|                |       | RX valid during USB receive, and TX Ready during USB       |

|                |       | transmit. The PHY also asserts nxt and dir                 |

|                |       | simultaneously to indicate USB receive activity            |

|                |       | (RXActive), if dir was previously low. The PHY is not      |

|                |       | allowed to assert nxt during the first cycle of the TX CMD |

|                | 0     | driven by the Link                                         |

| stp3           | OUT   | Output to ULPI PHY. The Link must assert stp to signal     |

|                |       | the end of a USB transmit packet or a register write       |

|                |       | operation, and optionally to stop any receive. The stp     |

|                |       | signal must be asserted in the cycle after the last data   |

| 1 . 2[7.0]     |       | byte is presented on the bus                               |

| data3[7:0]     | INOUT | 8 bit data bus. Driven to 00h by the Link when the         |

|                |       | ULPI bus is idle. The signals in this bus are synchronized |

|                |       | with positive edge of clk60                                |

**Table 2: OHCI DMA Interface Signals**

| Pin                   | Direction | Description                                              |

|-----------------------|-----------|----------------------------------------------------------|

| ahb_slv_active_n      | IN        | Indicates to the OHCI, that an external master accesses  |

|                       |           | this Slave. Asserted till the transfer completes         |

| ahb_slv_wr            | IN        | Register write to the OHCI target                        |

| ahb_slv_addr          | IN        | Address of the target register                           |

| h_data_out [31:0]     | OUT       | Register read data from OHCI                             |

| ahb_h_data_out [31:0] | IN        | Register write data to OHCI                              |

| b_cbe_in              | IN        | Command byte enable from master                          |

| omas_bus_req          | OUT       | OHCI request to system master core to perform DMA        |

| om_adstb_n            | OUT       | OHCI indicates the presence of DMA address on data lines |

| omas_rd_wr            | OUT       | Back end indicates to system master core to do a read or |

|                       |           | write operation                                          |

|                       |           | 0 - Read. 1 - Write                                      |

| omas_cbe_n [3:0]      | OUT       | OHCI provides byte enables for write transfer. Has same  |

|                       |           | timing as write data                                     |

| omas_device_ready     | OUT       | OHCI indicates that it is ready for DMA transfer. It     |

|                       |           | should not be deasserted before the DMA completes        |

| omas_final_dphase     | OUT       | Asserted by OHCI for last beat                           |

| ptop_m_func_rdy       | OUT       | Asserted by the system core whenever there is a          |

|                       |           | successful transfer                                      |

| ptop_m_pci_done       | OUT       | Asserted by the system core when the last beat for       |

|                       |           | current DMA ends                                         |

| clk                   | IN        | Operating clock frequency                                |

| clk_out               | IN        | USB interface clock frequency                            |

| reset_n               | IN        | Active low reset signal                                  |

# 2.6 SoC Level Integration

#### 2.6.1 Verification Environment

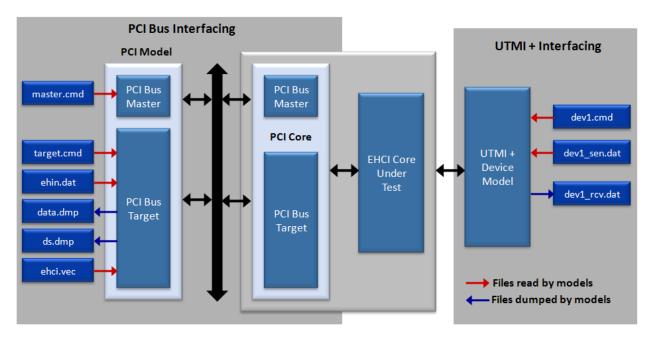

The Verification Environment used to verify the EHCI 2.0 DUT. This Verification Environment includes test suites to provide a complete verification solution for functional verification of EHCI 2.0 DUT. This Verification Environment consists of:

The EHCI is tested with PCI models and Device model. The PCI model has an address constraint that the address range for data, Qhead, QTd, IsoTd and SiTd are to be separate. This is to easily identify the memory dumping once a testcase's simulation is completed.

When a transaction is to be started by the Enhanced Host controller, the PCI model has to load the memory with data structure with Qhead and QTd in the corresponding locations.

The EHCI reads the data structure one by one and performs the USB transaction and updates the data structures in the same unique locations. The updated data structure as such is dumped in the file "ds.dmp".

The Verification Environment includes exhaustive built-in tests to verify the various functionalities of the EHCI 2.0 DUT.

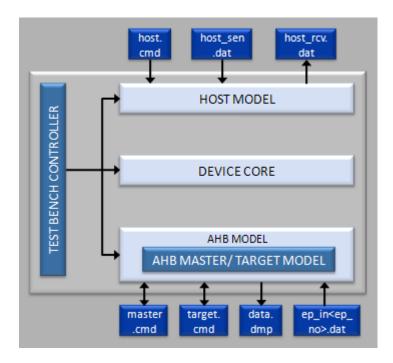

**Figure 4: Verification Environment**

#### 2.6.2 IP Deliverables

The IP package consists of the following:

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Simulation scripts

# 3 USB 2.0 Hub IP

# 3.1 Overview

The Universal Serial Bus (USB) is a type of serial bus that enables transfer of data between a host computer and various types of peripheral devices. The USB host has point-to-point connections with USB devices via a tiered star topology, in which each star contains a device called a hub. The USB enables connection of up to 127 devices via this tiered star topology. In addition, devices can be connected or disconnected while the system is still operating. All the above things are made possible via the USB2.0 Hub.

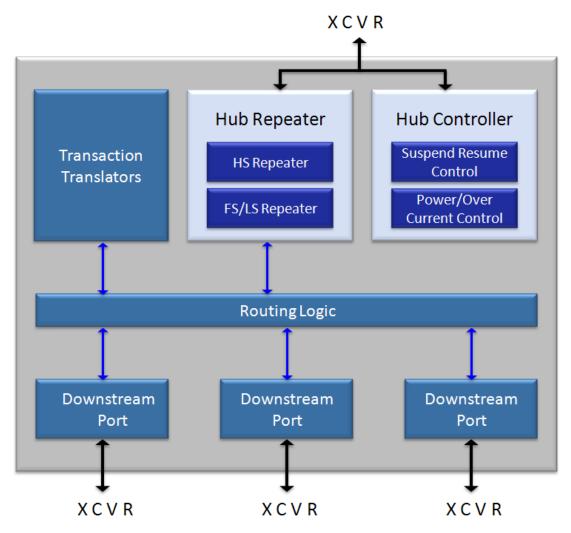

The Arasan USB 2.0 Hub IP core is an USB 2.0 specification compliant hub core that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode. The Arasan USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports. The major functions of the hub being device connection/disconnection detection, establishing upstream and downstream connectivity, enforcement of specific USB defined End-Of- Frame points over the bus and suspend/resume handling.

The USB 2.0 Hub core consists of Hub Repeater, Hub Controller and Transaction Translator. The Hub Controller provides the mechanism for host to hub communication. Hub specific status and control commands permit the host to configure a hub and to monitor and control its transaction translator and individual downstream ports.

The Hub Controller controls the operation of the USB hub by interpreting both the USB commands and Hub class specific commands. High-speed packets originated from the root hub are forwarded by the Hub Repeater to the HS Downstream Ports through the Routing Logic. Full-speed and low-speed packets scheduled by the host system software as split transactions are forwarded to the Transaction Translators.

The Transaction Translators handle split transactions that convey isochronous, interrupt, control, and bulk transfers across the high-speed bus to and from the full-speed and low-speed devices that attached to the hub. The Transaction Translators also perform CRC on incoming packets from the Hub Repeater or Routing Logic. The Routing Logic connects the Hub Repeater to the Downstream Ports in a high-speed transfer, and it connects the Transaction Translators to the Downstream Ports in a full-speed or low-speed transfer. The number of Downstream Ports is scalable.

# 3.2 Features

- High speed support: 480 Mbit/sFull speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI/ULPI interface

- UTMI Interface Clock: 30/60 MHz

- USB Suspend/Resume support

- Supports all hub specific requests

- UTMI and UTMI+ Txcvr compatible upstream and downstream support

- Technology and process independent

- Supports Remote wakeup features

- Parametrizable number of downstream ports

- Shared TT for the downstream ports for HS/FS/LS

- Supports suspend/resume for power management

- HS repeater for the downstream HS device

- FS/LS repeater for the downstream FS/LS device when Hub is connected to FS host upstream

- Downstream device connect / disconnect detection

# 3.3 Architecture

# 3.3.1 Functional Block Diagram

Figure 5: USB 2.0 HUB IP Core Functional Block Diagram

# 3.3.2 Functional Block Diagram Description

#### 3.3.2.1 Transaction Translators

This block isolates the high-speed bus from the full-speed bus using data buffers. Split transaction wrappers of the transactions meant for the full speed bus are removed and both the token and data packet for the full speed bus are stored inside the data buffer. The data buffer houses the status information from the full speed bus.

### 3.3.2.2 Hub Repeater

The hub repeater is a protocol controlled switch between the upstream and downstream ports. Hub repeaters also have hardware support for reset and suspend/resume handling. It also supports bus fault detection and recovery.

#### 3.3.2.3 HS Repeater

This block handles the broadcast of upstream data to downstream ports and also routes the downstream connectivity to the upstream. The repeater state machine block operating at 30Mhz (from the external clock) controls the repeater data path between the upstream ports and the downstream ports.

#### 3.3.2.4 FS/LS Repeater

This block handles the broadcast of upstream data to downstream ports and also routes the downstream connectivity to the upstream. The repeater state machine block operation at 60Mhz (from the external clock) controls the repeater data path between the upstream ports and the downstream ports.

#### 3.3.2.5 Hub Controller

The Controller provides the communication to/from the host. The information like Hub-specific status and control commands permit the host to configure a hub and to monitor and control its ports.

#### 3.3.2.6 Suspend Resume Control

The Hub Repeater is a protocol-controlled switch between the upstream port and downstream ports. It has the support for reset and suspend/resume signaling. Hub support's suspend and resume both as a USB device and in terms of propagating suspend and resume signaling. Hub supports both global and selective suspend and resume. Global suspend/resume refers to the entire bus being suspended or resumed without affecting any hub's downstream facing port states; selective suspend/resume refers to a downstream facing port of a hub being suspended or resumed without affecting the hub state.

### 3.3.2.7 Power/Over Current Control

The power management system may transition a device to the suspended state or power-off the device in order to control and conserve power. Power switch control and the over current protection of the downstream ports are implemented. The architecture supports individual port power switching and Gang mode.

### 3.3.2.8 Routing Logic

The operating speed of a device attached on a downstream facing port determines whether the Routing Logic connects a port to the Transaction Translator or Hub Repeater sections. When the hub upstream facing port is attached to an environment that is operating at high-speed, the full-

/low-speed hub repeater is not operational. Hence when a high-speed device is attached on downstream facing port, the routing logic connects the port to the hub repeater and the hub repeater operates as a high-speed repeater. When a full-/low-speed device is attached on a downstream facing port, the routing logic connects the port to the transaction translator.

#### 3.3.2.9 Downstream Port

This block implements the downstream ports state machine. It handles/reports the status of the downstream ports to the control endpoint and status change endpoint. This block operates at 30Mhz with serial data interface to the downstream ports.

# 3.4 Signal Interfaces

Table 3: HUB2.0 Upstream Port PIN Description

| Pin            | Direction | Description                                                |

|----------------|-----------|------------------------------------------------------------|

| pwr_on_rst     | Input     | Power on reset signal (asynchronous)                       |

| utm_clkout     | Input     | Clock. This output is used for clocking receive and        |

|                |           | transmit parallel data. 30 MHz HS/FS, with 16-bit          |

|                |           | interface                                                  |

| utm_rxvalid    | Input     | Receive Data Valid. Indicates that the utm_data bus has    |

|                |           | valid data. The Receive Data Holding Register is full and  |

|                |           | ready to be unloaded. The SIE is expected to latch the     |

|                |           | utm_data out bus on the clock edge                         |

| utm_rxactive   | Input     | Receive Active. Indicates that the receive state machine   |

|                |           | has detected SYNC and is active. utm_rxactive is negated   |

|                |           | after a Bit Stuff Error or an EOP is detected              |

| utm_rxerror    | Input     | Receive Error.                                             |

|                |           | 0 Indicates no error.                                      |

|                |           | 1 Indicates that a receive error has been detected         |

| utm_txready    | Input     | Transmit Data Ready. If is asserted, the SIE must always   |

|                |           | have data available for clocking in to the TX Holding      |

|                |           | Register on the rising edge of CLK.                        |

| linestate[1:0] | Input     | Line State. These signals reflect the current state of the |

|                |           | single ended receivers. They are combinatorial until a     |

|                |           | usable CLK is available then they are synchronized to      |

|                |           | CLK. They directly reflect the current state of the DP     |

|                |           | (Linestate[0]) and DM.(LineState[1]) signals:              |

|                |           | DM DP Description                                          |

|                |           | 0 0 0 : SE0                                                |

|                |           | 0 1 1 : 'J' State                                          |

|                |           | 1 0 2 : 'K' State                                          |

|                |           | 113:SE1                                                    |

| utm_data16_8   | Input     | Data Bus 16 - 8. Selects between 8 and 16 bit data         |

|                |           | transfers.                                                 |

|                |           | 1:16-bit data path operation enabled.                      |

|                |           | DataIn(8-15), DataOut(8-15), TXValidH, and RXValidH        |

|                  |              | operational. CLK = 30 MHz.                                                  |

|------------------|--------------|-----------------------------------------------------------------------------|

|                  |              | 0 : 8-bit data path operation enabled.                                      |

|                  |              | · · · · · · · · · · · · · · · · · · ·                                       |

|                  |              | DataIn(8-15),DataOut(8-15), TXValidH, and RXValidH undefined. CLK = 60 MHz. |

| utm_vevreal[1:0] | Output       | Transceiver Select. This signal selects between the FS                      |

| utm_xcvrsel[1:0] | Output       | and HS transceivers:                                                        |

|                  |              |                                                                             |

|                  |              | 0: HS transceiver enabled                                                   |

|                  |              | 1: FS transceiver enabled                                                   |

|                  |              | This signal is not provided in FS Only and LS Only                          |

| <u> </u>         |              | transceiver implementations                                                 |

| utm_termsel      | Output       | Termination Select. This signal selects between the FS                      |

|                  |              | and HS                                                                      |

|                  |              | terminations:                                                               |

|                  |              | 0: HS termination enabled                                                   |

|                  |              | 1: FS termination enabled                                                   |

|                  |              | This signal is not provided in FS Only and LS Only                          |

|                  |              | transceiver implementations                                                 |

| utm_reset        | Output       | Reset all state machine in UTM                                              |

| utm_suspendm     | Output       | Suspend. Places the Macrocell in a mode that draws                          |

|                  |              | minimal power from supplies. Shuts down all blocks not                      |

|                  |              | necessary for Suspend/ Resume operation. While                              |

|                  |              | suspended, utm_termsel must always be in FS mode to                         |

|                  |              | ensure that the 1.5K pull_up on DP remains powered.                         |

|                  |              | 0: Macrocell circuitry drawing suspend current                              |

|                  |              | 1: Macrocell circuitry drawing normal current                               |

| utm_opmode[1:0]  | Output       | Operational Mode. These signals select between various                      |

|                  |              | operational modes:                                                          |

|                  |              | [1] [0] Description                                                         |

|                  |              | 0 0 0: Normal Operation                                                     |

|                  |              | 0 1 1: Non-Driving                                                          |

|                  |              | 1 0 2: Disable Bit Stuffing and NRZI encoding                               |

|                  |              | 1 1 3: Reserved                                                             |

| utm txvalid      | Output       | Transmit Valid. Indicates that the DataIn bus is valid. The                 |

|                  |              | assertion of Transmit Valid initiates SYNC on the USB.                      |

|                  |              | The negation of Transmit Valid initiates EOP on the USB                     |

| utm_data[15:0]   | Input/Output | Utm databus. This is 16-bit parallel in/out data. Value of                  |

|                  |              | this data bus varied accordingly the signal                                 |

|                  |              | Utm_databus16_8. If the value of this signal is one                         |

|                  |              | means the utm_data will send the 16-bits of data,                           |

|                  |              | otherwise it sends 8-bits of data                                           |

| utm_validh       | Output       | validh. This signal that the higher order of the data_bus                   |

| vanan            | Jacpar       | is valid or not. When Databus16 8 is zero then the value                    |

|                  |              | of this signal is undefined. The status of the lower order                  |

|                  |              | byte is determined by Txvalid and Rxvalid                                   |

| ry do un         | Innut        |                                                                             |

| rx_dp_up         | Input        | Rx_DP. This is single ended receive data, positive                          |

|                  |              | terminal. The data is only valid if FsLsSerialMode is set to                |

|                  |              | 1b                                                                          |

| rx_dm_up        | Input  | Rx_DM. This is single ended receive data,negative terminal The data is only valid if FsLsSerialMode is set to 1b |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------|

| rx_rcv_dp       | Input  | Rx_RCV. Receive data. The data is only valid if FsLsSerialMode is set to 1b                                      |

| tx_enable_n_up  | Output | Tx_Enable_N. This is the active low output enable signal                                                         |

| tx_dat_up       | Output | Tx_DAT. Differential data at D+/D- output                                                                        |

| tx_se0_up       | Output | Tx_Se0. Force single ended zero                                                                                  |

| fslsserialmode_ | Input  | FsLsSerialMode. This signal is zero means FS and LS                                                              |

| up              |        | packets are sent using the parallel interface. One means                                                         |

|                 |        | FS and LS packets are sent using the serial interface                                                            |

Active low signals have been indicated with a suffix of '\_n'.

**NOTE:** The above indicated signals are for the upstream port of the USB Hub. These same signal set is used for downstream port of this USB Hub. In addition the following signals power and over current protection.

Table 4: HUB2.0 Downstream Port PIN Description

| Pin            | Direction | Description                                                                                                                                                                                                                                                                                                                      |

|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pwr_on_rst     | Input     | Power on reset signal (asynchronous)                                                                                                                                                                                                                                                                                             |

| utm_clkout     | Input     | Clock. This output is used for clocking receive and transmit parallel data. 30MHz HS/FS, with 16-bit interface                                                                                                                                                                                                                   |

| utm_rxvalid    | Input     | Receive Data Valid. Indicates that the utm_data bus has valid data. The Receive Data Holding Register is full and ready to be unloaded. The SIE is expected to latch the utm_data out bus on the clock edge                                                                                                                      |

| utm_rxactive   | Input     | Receive Active. Indicates that the receive state machine has detected SYNC and is active. utm_rxactive is negated after a Bit Stuff Error or an EOP is detected                                                                                                                                                                  |

| utm_txready    | Input     | Transmit Data Ready. If is asserted, the SIE must always have data available for clocking in to the TX Holding Register on the rising edge of CLK.                                                                                                                                                                               |

| linestate[1:0] | Input     | Line State. These signals reflect the current state of the single ended receivers.  They are combinatorial until a usable CLK is available then they are synchronized to CLK. They directly reflect the current state of the DP (Linestate[0]) and DM.(LineState[1]) signals:  DM DP Description  0 0 0 : SE0  0 1 1 : 'J' State |

|                  |              | 1 0 2 : 'K' State                                                           |

|------------------|--------------|-----------------------------------------------------------------------------|

|                  |              | 1 1 3 : SE1                                                                 |

| utm_data16_8     | Input        | Data Bus 16 - 8. Selects between 8 and 16 bit data                          |

|                  |              | transfers.                                                                  |

|                  |              | 1:16-bit data path operation enabled. DataIn(8-15),                         |

|                  |              | DataOut(8-15), TXValidH, and RXValidH operational.                          |

|                  |              | CLK = 30 MHz.                                                               |

|                  |              | 0:8-bit data path operation enabled. DataIn(8-                              |

|                  |              | 15),DataOut(8-15), TXValidH, and RXValidH unde-                             |

|                  |              | fined.CLK = 60 MHz.                                                         |

| utm_xcvrsel[1:0] | Output       | Transceiver Select. This signal selects between the FS                      |

|                  |              | and HS transceivers:                                                        |

|                  |              | 0: HS transceiver enabled                                                   |

|                  |              | 1: FS transceiver enabled                                                   |

|                  |              | This signal is not provided in FS Only and LS Only                          |

| tus taussal      | Outrout      | transceiver implementations                                                 |

| utm_termsel      | Output       | Termination Select. This signal selects between the FS and HS terminations: |

|                  |              | 0: HS termination enabled                                                   |

|                  |              | 1: FS termination enabled                                                   |

|                  |              | This signal is not provided in FS Only and LS Only                          |

|                  |              | transceiver implementations.                                                |

| utm_reset        | Output       | Reset all statemachine in UTM.                                              |

| utm_suspendm     | Output       | Suspend. Places the Macrocell in a mode that draws                          |

| atin_suspendin   | Output       | minimal power from supplies. Shuts down all blocks                          |

|                  |              | not necessary for Suspend/                                                  |

|                  |              | Resume operation. While suspended, utm_termsel                              |

|                  |              | must always be in FS mode to ensure that the 1.5K                           |

|                  |              | pull_up on DP remains powered.                                              |

|                  |              | 0: Macrocell circuitry drawing suspend current                              |

|                  |              | 1: Macrocell circuitry drawing normal current                               |

| utm_opmode[1:    | Output       | Operational Mode. These signals select between                              |

| 0]               |              | various operational modes:                                                  |

|                  |              | [1] [0] Description                                                         |

|                  |              | 0 0 0: Normal Operation                                                     |

|                  |              | 0 1 1: Non-Driving                                                          |

|                  |              | 1 0 2: Disable Bit Stuffing and NRZI encoding                               |

|                  |              | 1 1 3: Reserved.                                                            |

| utm_txvalid      | Output       | Transmit Valid. Indicates that the DataIn bus is valid.                     |

|                  |              | The assertion of Transmit Valid initiates SYNC on the                       |

|                  |              | USB. The negation of Transmit Valid initiates EOP on                        |

|                  |              | the USB.                                                                    |

| utm_data[15:0]   | Input/Output | Utm_databus. This is 16-bit parallel in/out data. Value                     |

|                  |              | of this data bus varied accordingly the signal                              |

|                  |              | Utm_databus16_8. If the value of this signal is one                         |

|                  |              | means the utm_data will send the 16-bits of data,                           |

|                  |              | otherwise it sends 8-bits of data.                                          |

|                 | 1      |                                                           |

|-----------------|--------|-----------------------------------------------------------|

| utm_validh      | Output | validh. This signal that the higher order of the          |

|                 |        | data_bus is valid or not. When Databus16_8 is zero        |

|                 |        | then the value of this signal is undefined. The status of |

|                 |        | the lower order byte is determined by Txvalid and         |

|                 |        | Rxvalid.                                                  |

| rx_dp_up        | Input  | Rx_DP. This is single ended receive data,positive         |

|                 |        | terminal. The data is only valid if FsLsSerialMode is set |

|                 |        | to 1b                                                     |

| rx_dm_up        | Input  | Rx_DM. This is single ended receive data,negative         |

|                 |        | terminal The data is only valid if FsLsSerialMode is set  |

|                 |        | to 1b                                                     |

| rx_rcv_dp       | Input  | Rx_RCV. Receive data. The data is only valid if           |

|                 |        | FsLsSerialMode is set to 1b                               |

| tx_enable_n_up  | Output | Tx_Enable_N. This is the active low output enable         |

|                 |        | signal                                                    |

| tx_dat_up       | Output | Tx_DAT. Differential data at D+/D- output                 |

| tx_se0_up       | Output | Tx_Se0. Force single ended zero                           |

| fslsserialmode_ | Input  | FsLsSerialMode. This signal is zero means FS and LS       |

| up              |        | packets are sent using the parallel interface. One        |

|                 |        | means FS and LS packets are sent using the serial         |

|                 |        | interface                                                 |

| turn_power_on   | Output | This signal is used for the external power supply to      |

|                 |        | provide power to the downstream port                      |

| over_curr_indic | Input  | This signal is asserted if an over current was detected   |

# 3.5 SoC Level Integration

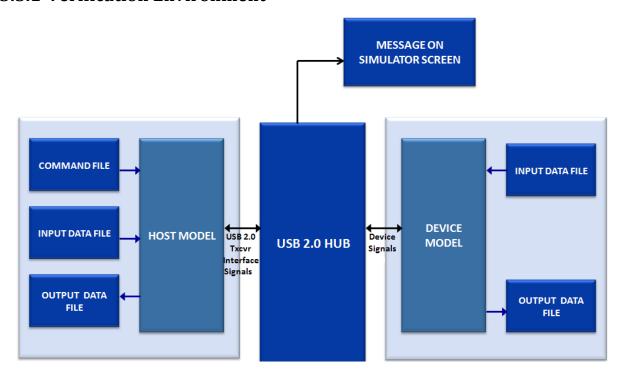

### 3.5.1 Verification Environment

**Figure 6: RTL Verification Environment**

### 3.5.2 IP Deliverables

The IP package consists of the following:

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Simulation scripts

# 4 USB 2.0 Device IP

### 4.1 Overview

The USB 2.0 Device IP core is enables designers in the PC, mobile, consumer and communication markets to bring significant power and performance enhancements to the popular USB standard while offering compatibility with billions of USB-enabled devices currently in the market.

The Arasan USB 2.0 compliant Device core is available with an AHB/AXI, OCP or custom system bus interface. The USB2.0 device core supports 480 Mbits/s in High Speed (HS) mode and 12 Mbits/s in Full Speed (FS) mode of operation. Arasan provides designers with a comprehensive, silicon-proven configurable digital USB 2.0 Device solution that conforms to the USB 2.0 specification. It is designed to seamlessly integrate into any SoC design for an easy and cost effective solution. The Arasan USB 2.0 IP core supports up to 30 configurable IN/OUT non-control endpoints.

Each non-control endpoint has a controller for supporting interrupt, bulk and isochronous transfers. The dedicated control endpoint 0 handles USB defined command structure for Device Control. The USB 2.0 Device IP includes a multi-channel DMA that can be configured to access any endpoint through registers. Optionally, it can interface with an external DMA controller. The Device IP core provides an UTMI+/ULPI interface that allows connection to any USB 2.0 transceiver module.

### 4.2 Features

- High speed support: 480 Mbit/s

- Full speed support: 12 Mbit/s

- USB 2.0 Compliant

- High/Full speed support using 8/16 bit UTMI+/ULPI interface

- Master DMA implementation for each endpoint

- Optional PIO Mode for each endpoint (can be used for Interrupt endpoints)

- System bus Master/Target clock

- UTMI+ Interface Clock: 30/60 MHz

- Endpoint Configuration

- Configurable up to 15 Tx and Rx endpoints

- Configuration options: Bulk, control, isochronous, interrupt

- Dedicated control endpoint zero

- Configurable dual port RAM shared between endpoints

- USB Suspend/Resume support

- 32/64 bit AXI, AHB or OCP bus interfaces

- Interfaces between USB 2.0 bus and the User bus.

- Supports 16-bit UTMI+ /8-bit ULPI Interface to USB2.0 Transceiver.

- Support direct register addressing for all registers from the User bus.

- Software control for device remote-wakeup.

- User bus facilitates connection to common microcontrollers and DMA controllers.

- Three different modes of operation of an in-endpoint (Auto validation mode, manual validation mode, Fly mode)

- Supports standard 16-bit transfers on the User bus

- Supports Endpoint Maximum Packet Size up to 1024 bytes.

### 4.3 Architecture

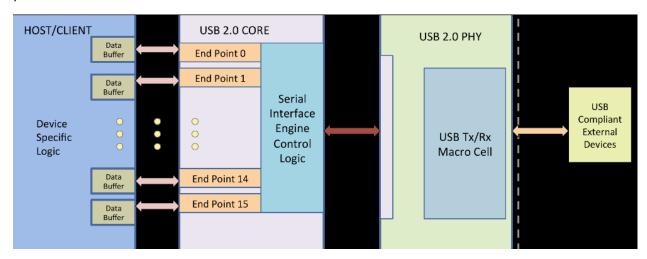

### 4.3.1 Functional Block Diagram

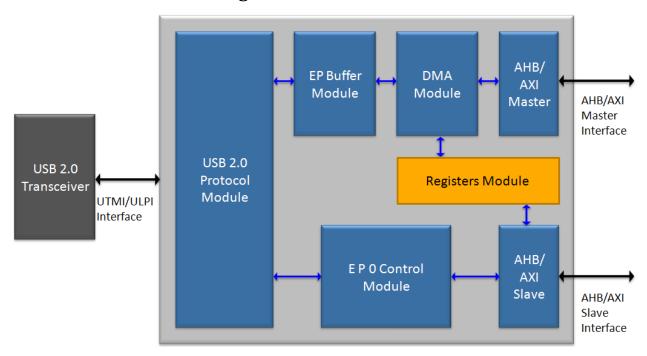

Figure 7: USB 2.0 Device IP Core Block Diagram

# 4.3.2 Functional Block Diagram Description

#### 4.3.2.1 USB 2.0 Protocol Module

The parallel interface engine supports all USB protocols. The reset, suspend and resume sequence are taken care by this block. The PID decoding and PID encoding for the data packets and handshake are done in this block. The transmission as well as reception of packets is handled by this block. The CRC generation and checking for the transmission and reception of data packets are done by this module.

#### 4.3.2.2 EP Buffer Module

Endpoint RAM operation is controlled by this Endpoint Buffer block. This block generates the read and writes control signals to access and dump the data inside the RAM. The read/ write pointers access is shared by USB side as well as backend side.

#### **4.3.2.3 DMA Module**

The DMA read and write operation control is taken care of this block. Read/Write operation is based on the internal FIFO status. Whenever the OUT endpoint FIFO data is available (Max packet size or short packet), this block will initiate the dma\_req to the external interface to perform the DMA Write to the external memory. For IN endpoint whenever the endpoint FIFO is empty the dma\_req signal will be initiated to perform DMA read from the external memory. This block uses clk30 for its operation.

#### 4.3.2.4 Registers Module

This block holds all the internal posts registers namely Main Control, USB Control, Control Endpoint, Non-Control Endpoint and DMA registers. The register configuration is handled inside the block and also provides control signals to all other blocks. This block uses transceiver clk30 for its operation.

#### 4.3.2.5 AHB/AXI Master Interface

This block performs AHB Master Function with respect to the Backend Interface. Whenever the device wants to perform a data transfer to/from system memory to the USB, it acts as a master.

#### 4.3.2.6 AHB/AXI Slave Interface

This module provides the interface to access the function registers. With this interface, the configuration of End points and the handling of standard device requests of the Device controller take place through AHB/AXI bus.

#### 4.3.2.7 EPO Controller Module

Endpoint zero has special significance in a USB system. It is a CONTROL endpoint, and it is required by every USB device. The USB host uses special SETUP tokens to signal transfers that deal with device control; only CONTROL endpoints accept these special tokens. The USB host sends a suite of standard device requests over endpoint zero.

# 4.4 Pin Details

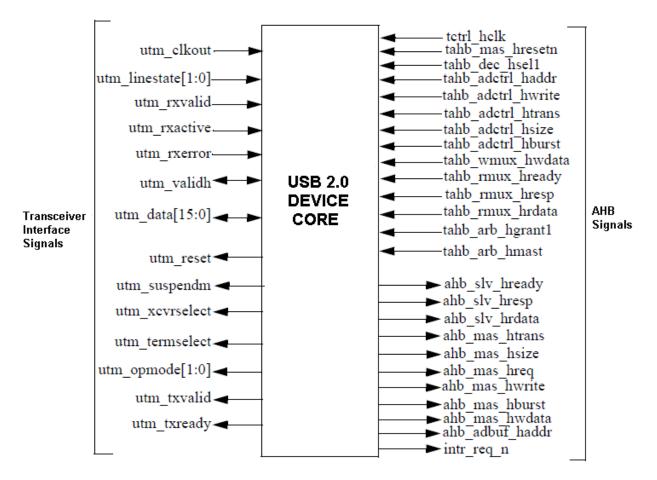

Figure 8: Pinout Diagram

# 4.5 Signal Interfaces

The USB 2.0 IP Core has the following interfaces:

- UTMI+/ULPI Interface

- AHB Interface

# 4.5.1 UTMI+/ULPI Interface

The high speed and full speed support in the USB end is provided by the UTMI+/ULPI interface. An 8 bit UTMI+ interface with 60 MHz is preferred, since the migration to ULPI is easy. Additionally, a UTMI+ to ULPI wrapper is provided as an option, in order to support low pin count external USB 2.0 PHY. Also, OTG support can be added for USB 2.0 using this interface.

Table 5: UTMI+ Interface Signals

| Pin               | Direction | Description                                                         |

|-------------------|-----------|---------------------------------------------------------------------|

| utm_clkout        | IN        | All the outputs get asserted synchronous to the rising              |

|                   |           | edge of this clock only.                                            |

| utm_rxvalid       | IN        | Signal indicating that the lower byte of data bus from              |

|                   |           | the transceiver contains valid data.                                |

| utm_rxactive      | IN        | Signal indicating that SYNC has been detected and the               |

|                   |           | packet bytes will follow. It gets deasserted after an EOP           |

|                   |           | is detected                                                         |

| utm_rxerror       | IN        | Signal indicating that there is packet error in the                 |

|                   |           | received packet.                                                    |

| utm_txready       | IN        | Signal indicating that the transceiver has clocked the              |

|                   |           | data from the bus and is ready for the next transfer on             |

|                   |           | the bus. Used as handshake signal for utm_txvalid from              |

|                   |           | device.                                                             |

| utm_linestate     | IN        | These signals reflect the current state of the USB bus              |

| utm_validh        | INOUT     | When asserted, it means that the data[15:0] are valid               |

| utm_reset         | OUT       | Signal used to reset all state machines of the transceiver.         |

| utm_xcvrselect    | OUT       | This signal selects between the FS and HS transceivers.             |

|                   |           | This signal along with the signal utm_termselect is used            |

|                   |           | to indicate the speed of device operation                           |

| utm_termselect    | OUT       | This signal selects between the FS and HS terminations.             |

|                   |           | This signal along with the signal utm_xcvrselect is used            |

|                   |           | to indicate the speed of device operation.                          |

| utm_opmode        | OUT       | These signals are used by the transceiver to                        |

|                   |           | select between different operating modes as                         |

|                   |           | follows                                                             |

|                   |           | 00 - Normal Operation                                               |

|                   |           | 01 - Non - driving                                                  |

|                   |           | 10 - Disable Bit - Stuffing and NRZI                                |

|                   |           | encoding                                                            |

| utm database16 0  | OUT       | 11 - Reserved                                                       |

| utm_databus16_8   | 001       | Signal used to indicate 8-bit or 16-bit mode of operation           |

|                   |           | to the transceiver. Tied to '1' to support 16-bit mode of operation |

| utm_suspendm      | OUT       | Signal used to place the transceiver in a suspend                   |

| utiii_suspellulli |           | mode                                                                |

| utm_txvalid       | OUT       | Signal to indicate a packet transmission is to be initiated         |

| utiii_txvaiiu     |           | and the lower byte of data bus has valid data.                      |

|                   |           | and the lower byte of data bus has valid data.                      |

**Table 6: AHB Interface Signals**

| Pin                      | Direction | Description                                                  |

|--------------------------|-----------|--------------------------------------------------------------|

| tctrl_hclk               | IN        | All outputs are synchronous to the rising edge of this       |

|                          |           | clock. Inputs are sampled at the positive going edge of      |

|                          |           | this clock.                                                  |

| tahb_mas_hresetn         | IN        | This is the system reset to be given to the core. It is an   |

|                          |           | active low signal.                                           |

| tahb_dec_hsel1           | IN        | This signal indicates that the current transfer is intended  |

| <b>- -</b>               |           | for the selected slave.                                      |

| tahb_adctrl_haddr        | IN        | The 32-bit system address bus                                |

| tahb_adctrl_hwrite       | IN        | When HIGH this signal indicates a write transfer and         |

|                          |           | when LOW a read transfer                                     |

| tahb_adctrl_htrans[1:0]  | IN        | 2-bit encoded signal that indicates to the slave about the   |

|                          |           | type of transfer initiated by the master. The encoding is    |

|                          |           | similar to the one specified in the AMBA-AHB                 |

|                          |           | specification.                                               |

|                          |           | It is as follows:-                                           |

|                          |           | 00b IDLE                                                     |

|                          |           | 01b BUSY                                                     |

|                          |           | 10b NONSEQ                                                   |

|                          |           | 11b SEQ                                                      |

| ahb_adctrl_hsize [2:0]   | IN        | This input indicates the size of the transfer. In other      |

|                          |           | words, this indicates the no. of valid bytes in the data     |

|                          |           | bus.                                                         |

| tahb_adctrl_hburst [2:0] | IN        | This 3-bit encoded input provides the slave,                 |

|                          |           | the information on whether the transfer initiated is a       |

|                          |           | burst and the kind of burst transfer                         |

| tahb_wmux_hwdata[31:0]   | IN        | This 32-bit input is the wdata bus using                     |

|                          |           | which the master writes data into the target                 |

|                          |           | register/memory                                              |

| tahb_rmux_hready         | IN        | Active high signal indicating the readiness of the           |

|                          |           | selected slave to complete the current transfer              |

| tahb_rmux_hresp [1:0]    | IN        | 2-bit encoded input that provides the information            |

|                          |           | about the status of the current transfer                     |

| tahb_rmux_hrdata [31:0]  | IN        | 32-bit data bus that provides the read data                  |

|                          |           | from the selected slave                                      |

| tahb_arb_hgrant1         | IN        | Active high signal indicating that the core master has       |

|                          |           | been granted use of the bus                                  |

| tahb_arb_hmast[3:0]      | IN        | It is the Master number which is currently                   |

|                          |           | executing the transactions                                   |

| ahb_slv_hready           | OUT       | When high indicates that the slave is ready to complete      |

|                          |           | the current transfer. The slave shall de-assert this signal, |

|                          |           | in order to insert wait states on the bus                    |

| ahb_slv_hresp[1:0]       | OUT       | This 2-bit output bus is used by the slave to provide the    |

|                          |           | status of the transfer. The encoding is as follows           |

|                          |           | 00b OKAY                                                     |

|                        | 1   |                                                             |

|------------------------|-----|-------------------------------------------------------------|

|                        |     | 01b ERROR                                                   |

|                        |     | 10b RETRY                                                   |

|                        |     | 11b SPLIT                                                   |

| ahb_slv_hrdata[31:0]   | OUT | 32-bit output data bus used by the slave to return data     |

|                        |     | on master reads                                             |

| ahb_mas_htrans[1:0]    | OUT | A 2-bit encoded signal describing the type of transfer in   |

|                        |     | progress viz., nonseq, seq, idle or busy. This is needed to |

|                        |     | check whether the address buffer is required to             |

|                        |     | increment to the next sequential address or not             |

| ahb_mas_hsize[2:0]     | OUT | This input indicates the size of the transfer. In other     |

|                        |     | words, this indicates the no. of valid bytes in the data    |

|                        |     | bus                                                         |

| ahb_mas_hreq           | OUT | Active high signal indicating to the arbiter that this      |

|                        |     | master(core), needs use of the bus                          |

| ahb_mas_hwrite         | OUT | Active high signal indicating that the master intends to    |

|                        |     | do a write transfer                                         |

| ahb_mas_hburst [2:0]   | OUT | This 3-bit encoded input provides the slave, the            |

|                        |     | information on whether the transfer initiated is a burst    |