# Datasheet

SD 3.0/SDIO 3.0/eMMC v4.51 Total IP Solution

# Arasan Chip Systems Inc.

2010 North First Street, Suite #510, San Jose, CA 95131

Ph: 408-282-1600 Fax: 408-282-7800 www.arasan.com

#### **Disclaimer**

This document is written in good faith with the intent to assist the readers in the use of the product. Circuit diagrams and other information relating to Arasan Chip Systems' products are included as a means of illustrating typical applications. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. Information contained in this document is subject to continuous improvement and development.

Arasan Chip Systems' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Arasan Chip Systems Inc. will be fully at the risk of the customer.

Arasan Chip Systems Inc. disclaims and excludes any and all warranties, including, without limitation, any and all implied warranties of merchantability, fitness for a particular purpose, title, and infringement and the like, and any and all warranties arising from any course or dealing or usage of trade.

This document may not be copied, reproduced, or transmitted to others in any manner. Nor may any use of information in this document be made, except for the specific purposes for which it is transmitted to the recipient, without the prior written consent of Arasan Chip Systems Inc. This specification is subject to change at any time without notice. Arasan Chip Systems Inc. is not responsible for any errors contained herein.

In no event shall Arasan Chip Systems Inc. be liable for any direct, indirect, incidental, special, punitive, or consequential damages; or for loss of data, profits, savings or revenues of any kind; regardless of the form of action, whether based on contract; tort; negligence of Arasan Chip Systems Inc or others; strict liability; breach of warranty; or otherwise; whether or not any remedy of buyers is held to have failed of its essential purpose, and whether or not Arasan Chip Systems Inc. has been advised of the possibility of such damages.

#### **Restricted Rights**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

#### **Copyright Notice**

No part of this specification may be reproduced in any form or means, without the prior written consent of Arasan Chip Systems, Inc.

Questions or comments may be directed to:

Arasan Chip Systems Inc. 2010 North First Street, Suite 510 San Jose, CA 95131

Ph: 408-282-1600 Fax: 408-282-7800

Email: sales@arasan.com

# Contents

| 1 | Intr | oductior   | n                                        | 1  |

|---|------|------------|------------------------------------------|----|

|   | 1.1  | About eN   | 1MC                                      |    |

|   | 1.2  | Arasan's ( | Contribution to JEDEC and SD Association | 1  |

|   | 1.3  |            | Total IP Solution                        |    |

| 2 | S.D. | ט עלטוט    | 3.0/eMMC 4.51 Host Controller IP         | 1  |

| _ | 30   |            |                                          |    |

|   | 2.1  |            | /                                        |    |

|   | 2.2  |            |                                          |    |

|   | 2.3  |            | ure                                      |    |

|   | 2.3. |            | tional Description                       |    |

|   | 2.3. |            | tional Block Diagram                     |    |

|   | 2.3. |            | tional Block Diagram Description         |    |

|   | 2.4  |            |                                          |    |

|   | 2.4. |            | Description                              |    |

|   | 2.5  |            | Integration                              |    |

|   | 2.5. |            | eliverables for RTL Version              |    |

|   | 2.5. | 2 Verifi   | ication Environment                      | 20 |

| 3 | SDI  | O 3.0 De   | evice Controller IP                      | 22 |

|   | 3.1  | Overview   | /                                        | 22 |

|   | 3.2  |            |                                          |    |

|   | 3.3  |            | logy                                     |    |

|   | 3.4  | -          | ure                                      |    |

|   | 3.4. |            | tional Block Diagram Description         |    |

|   | 3.5  |            |                                          |    |

|   | 3.6  | _          | Integration                              |    |

|   | 3.6. |            | liverables                               |    |

|   | 3.6. |            | ication Environment                      |    |

|   | CD.  |            |                                          |    |

| 4 | SD/  | SDIO 3 L   | Device Controller IP                     | 31 |

|   | 4.1  | Overview   | /                                        | 31 |

|   | 4.2  | Features.  |                                          | 31 |

|   | 4.3  | Bus Topo   | logy                                     | 32 |

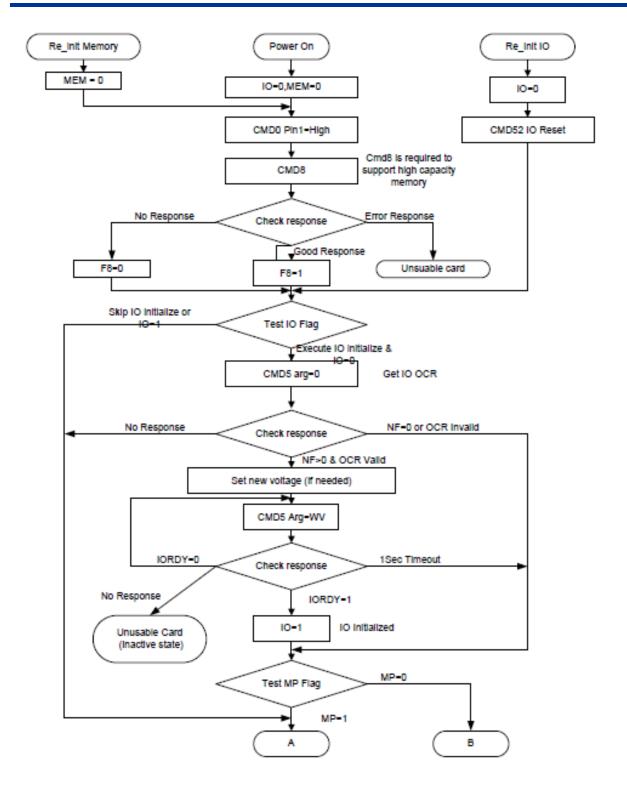

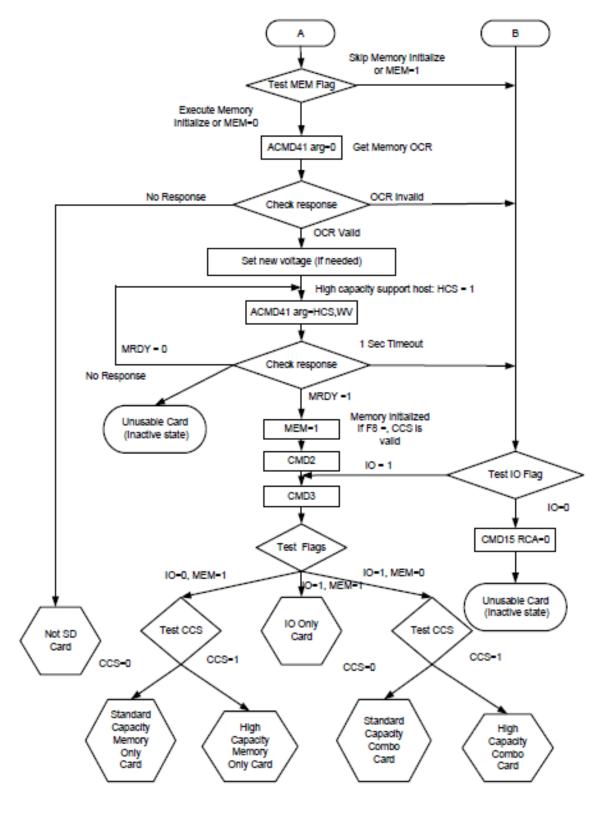

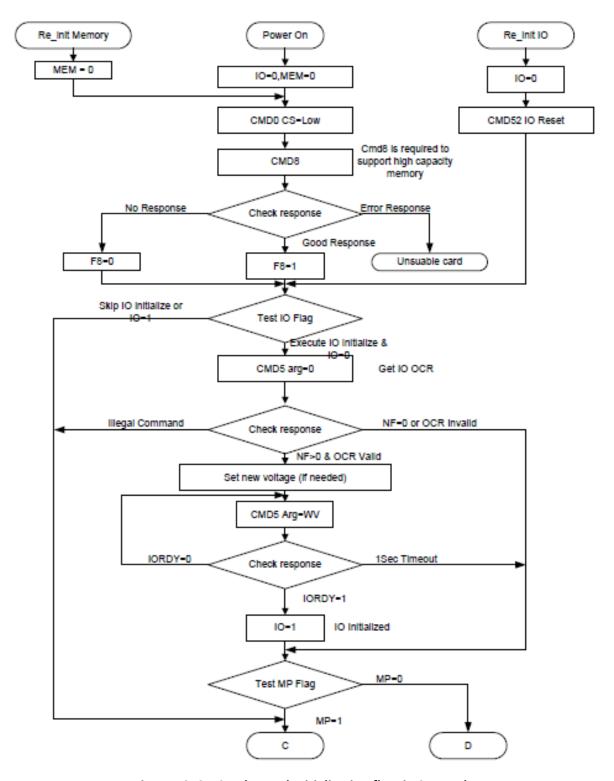

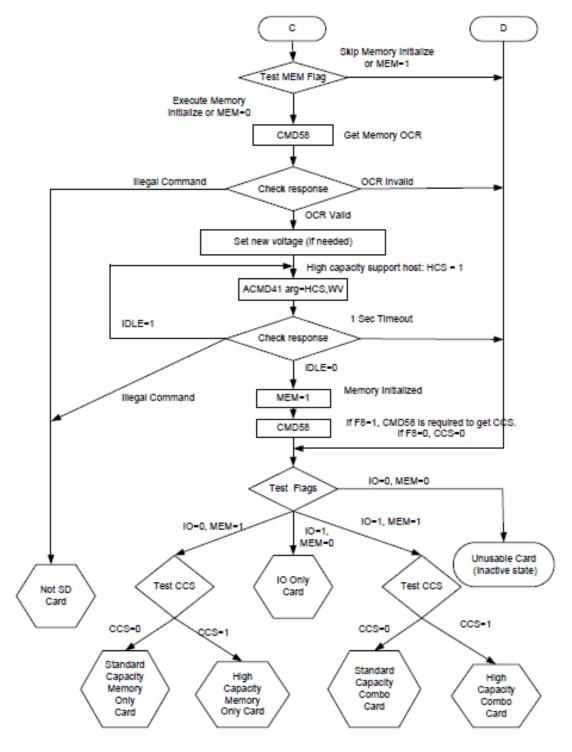

|   | 4.3. | L SD-Co    | ombo Card Initialization Sequence        | 33 |

|   | 4.4  | Architect  | ure                                      | 39 |

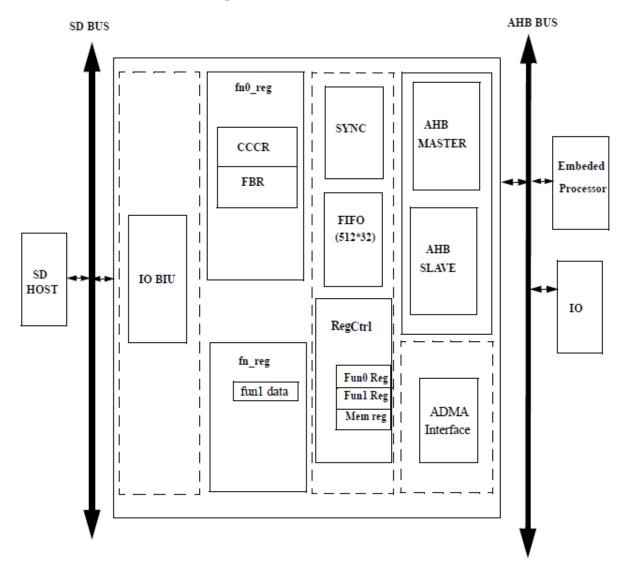

|   | 4.4. | L Funct    | tional Block Diagram                     | 39 |

|   | 4.4. | 2 Funct    | tional Block Diagram Description         | 40 |

|   | 4.5  | Signals    |                                          | 41 |

|   | 4.5. | L Signa    | al Interfaces                            | 41 |

|          | 4.6                         | SoC Level Integration                                 |        |

|----------|-----------------------------|-------------------------------------------------------|--------|

|          | 4.6.                        |                                                       |        |

| 5        | eM                          | MC 4.51 Device Controller IP                          | 45     |

|          | 5.1                         | Overview                                              |        |

|          | 5.2                         | Features                                              | 45     |

|          | 5.3                         | Architecture                                          | 47     |

|          | 5.3.                        | 1 Functional Description                              | 47     |

|          | 5.3.                        | 2 Functional Block Diagram                            | 47     |

|          | 5.3.                        | 3 Functional Block Diagram Description                | 48     |

|          | 5.4                         | Signal Interfaces                                     | 49     |

|          | 5.5                         | SOC Level Integration                                 | 53     |

|          | 5.5.                        | 1 Verification Environment                            | 53     |

|          | 5.5.                        | 2 Verification Deliverables                           | 53     |

|          | 5.5.                        | 3 IP Deliverables                                     | 53     |

| 6        | Har                         | dware Validation Platform                             | 54     |

| U        |                             |                                                       |        |

|          | 6.1                         | Overview                                              |        |

|          | 6.2                         | Features                                              | 54     |

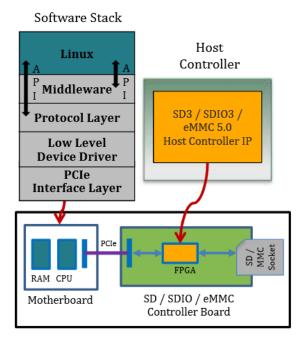

|          | 6.3                         | HVP Architecture                                      | 55     |

|          | 6.4                         | Deliverables                                          | 56     |

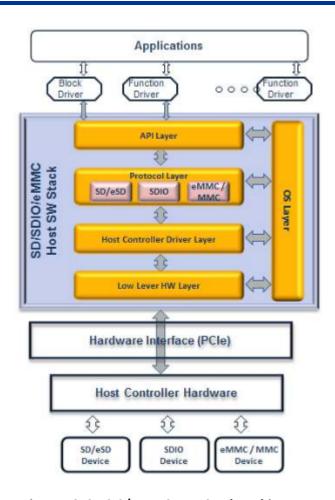

| 7        | SD                          | 3.0/SDIO 3.0/eMMC 4.51 Host Controller Software Stack | 57     |

|          | 7.1                         | Overview                                              | 57     |

|          | 7.2                         | Features                                              |        |

|          | 7.3                         | Architecture                                          |        |

|          | 7.4                         | Deliverables                                          |        |

|          |                             |                                                       |        |

| 8        | Ser                         | vices & Support                                       | 60     |

|          | 8.1                         | Global Support                                        | 60     |

|          | 8.2                         | Arasan Support Team                                   | 60     |

|          | 8.3                         | Professional Services & Customization                 | 60     |

|          | 8.4                         | The Arasan Porting Engine                             | 60     |

|          | 8.5                         | Pricing & Licensing                                   |        |

|          |                             | Fricing & Licensing                                   | 60     |

|          |                             | riidiig & Licensing                                   |        |

| T        | ahl-                        |                                                       | 60     |

| T        | able                        |                                                       | 60     |

|          |                             |                                                       |        |

| Ta       | ble 1: /                    | S                                                     | 9      |

| Ta<br>Ta | ble 1: <i>i</i><br>ble 2: 0 | S  AHB Bus Interface Signals                          | 9<br>9 |

| Table 5: Power Control Signals (Used for SD/SDIO Mode only)                  | 15 |

|------------------------------------------------------------------------------|----|

| Table 6: Clock, Special Controls and Test Mode Signals                       | 15 |

| Table 7: Block RAM (SRAM) Interface Signals                                  | 16 |

| Table 8: Core Configuration Signals                                          | 17 |

| Table 9: SD Interface Signals                                                | 28 |

| Table 10: AHB Slave Interface Signals                                        | 29 |

| Table 11: AHB Master Interface Signals                                       | 29 |

| Table 12: System Interface Signals                                           | 30 |

| Table 13: SD Interface Signals                                               | 42 |

| Table 14: AHB Slave Interface Signals                                        | 42 |

| Table 15: AHB Master Interface Signals                                       | 43 |

| Table 16: System Interface Signals                                           | 43 |

| Table 17: eMMC Bus Interface Signals                                         | 49 |

| Table 18: AHB Target Interface Signals:                                      | 50 |

| Table 19: AHB Master Interface Signals                                       | 50 |

| Table 20: 128x32 Dual-Port RAM1 Interface Signals                            | 51 |

| Table 21: 128x32 Dual-Port RAM2 Interface Signals                            | 52 |

| Table 22: 128x32 RAM Interface Signals                                       | 52 |

| Figures                                                                      |    |

| Figure 1: Arasan's Total IP Solution                                         | 3  |

| Figure 2: eMMC5.1/SD3.0/SDIO3.0 Host Controller Functional Block Diagram     | 6  |

| Figure 3: Verification Environment                                           | 21 |

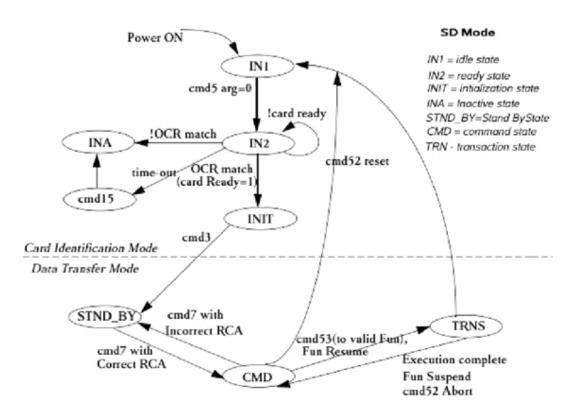

| Figure 4: SDIO Card Initialization Sequence for SD Mode                      | 24 |

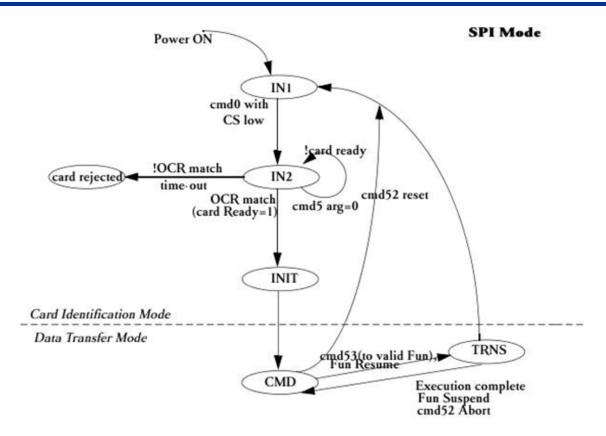

| Figure 5: SDIO Card Initialization Sequence for SPI Mode                     | 25 |

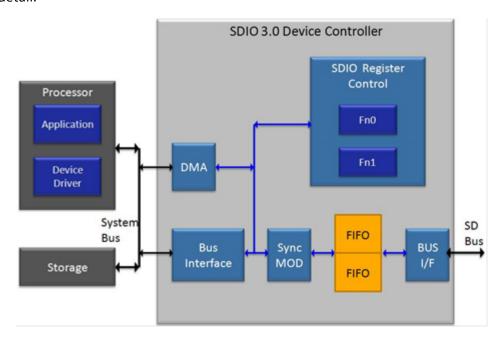

| Figure 6: SDIO3.0 Device Controller Architecture                             | 26 |

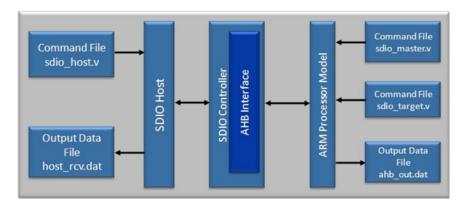

| Figure 7: Verification Environment of SDIO Controller IP with AHB System Bus | 30 |

| Figure 8: SD Combo card initialization flow in SD mode                       | 34 |

| Figure 9: SD Combo card initialization flow in SD mode Continued             | 35 |

| Figure 10: SD Combo card Initialization flow in SPI mode                     |    |

| Figure 11: SD Combo card Initialization flow in SPI mode Continued           | 38 |

| Figure 12: SD_Combo_AHB Architecture                                         | 39 |

| Figure 13: eMMC 4.51 Device Controller Functional Block Diagram              | 47 |

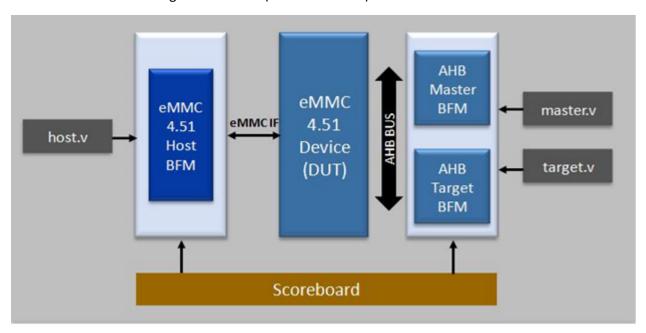

| Figure 14: Verification Environment of eMMC 4.51 Device                      |    |

| Figure 15: SD/SDIO/eMMC HVP Architecture                                     | 55 |

| Figure 16: SD 3.0/eMMC 4.51 Stack Architecture                               | 59 |

# 1 Introduction

# 1.1 About eMMC

eMMC, short for "embedded Multi-Media Card", is an embedded non-volatile memory system, comprised of both flash memory and a flash memory controller integrated in the same industry-standard BGA package.

eMMC architecture, integrating the flash memory and controller in the same package, simplifies the application interface design and frees the host processor from low-level flash memory management. This benefits product developers by simplifying the non-volatile memory interface design and qualification process – resulting in reducing time-to-market, as well as future proofing against new flash memory technology advances.

The eMMC standard has been developed and published by JEDEC™ Solid State Technology Association (www.jedec.org), the global leader in the development of standards for the microelectronics industry. JEDEC has over 4,000 participants, representing nearly 300 companies, working together in 50 JEDEC committees.

The latest revision of the JEDEC standard is 5.0, released on Sep. 2013, and defines a maximum bandwidth of 400 MB/s over 8 data lanes. The combination of 200 MHz DDR clock rate, and 8 data lanes, requires the use of a hard PHY. Arasan has designed the analog PHY in 40nm, 28nm, and 16nm FinFET+ process technologies, and are all silicon proven. Latest eMMC revision of the JEDEC about to be released is eMMC5.1 (Item # JC-64.1-67.14).

# 1.2 Arasan's Contribution to JEDEC and SD Association

Arasan Chip Systems has been an executive member with the Multi Media Card Association (MMCA) since 2002. The MMCA was later merged with JEDEC in 2008 as the emphasis of MMCA shifted from removable storage to embedded storage for mobile devices. Arasan is currently a contributing member to JEDEC actively promoting both the eMMC and UFS standards. Arasan is also a contributing member to the SD Association since 2001.

Arasan is the leader of mobile storage, with 300 IP licensees since 2002 for SD, SDIO, NAND, eMMC and UFS. Our eMMC Host and Device IPs were licensed to both Application Processor companies like Intel, LG, Samsung and Huawei, as well as the majority of the Memory companies, and includes SK Hynix, among others.

Arasan's active involvement and contribution to the relevant standards bodies, lead to deep domain expertise, which in turn results in early availability of high quality IP for our customers.

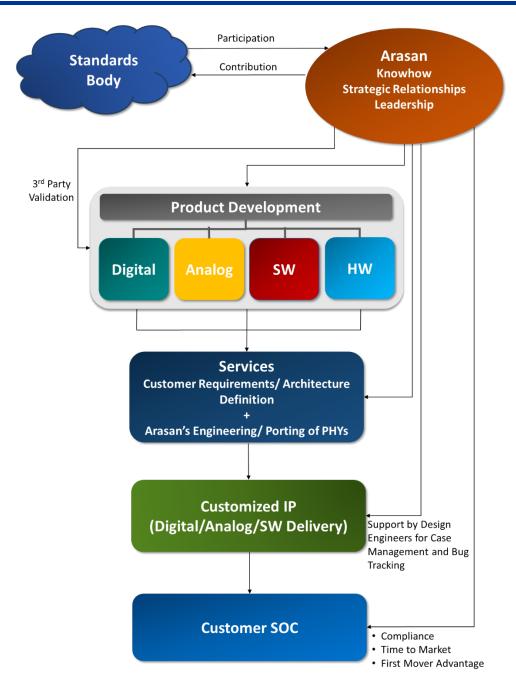

# 1.3 Arasan's Total IP Solution

Arasan provides a Total IP Solution, which encompasses all aspects of IP development and integration, including analog and digital IP cores, verification IP, software stacks & drivers, and hardware validation platforms.

#### Benefits of Total IP Solution:

- Seamless integration from PHY to Software

- Assured compliance across all components

- Single point of support

- Easiest acquisition process (one licensing source)

- Lowest overall cost including cost of integration

- Lowest risk for fast time to market

Figure 1: Arasan's Total IP Solution

# 2 SD 3.0/SDIO 3.0/eMMC 4.51 Host Controller IP

# 2.1 Overview

Arasan Chip Systems' SD 3.0/SDIO 3.0/eMMC 4.51 Host Controller IP is a highly integrated Intellectual Property (IP) solution that supports three key memory and I/O technologies:

- 1. SDA Secured Digital (SD) 3.0

- 2. SDA Secured Digital Input Output (SDIO) 3.0

- 3. JEDEC eMMC 4.51

This IP handles all the timing and interface protocol requirements to access these media as well as processing the commands in hardware.

The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC device, thereby simplifying system initialization during power up. The host interface is based on a standard 32-bit Advanced High-Performance Bus (AHB) which is used to transfer data and configure the IP.

## 2.2 Features

- Compliant with the following specifications:

- SDA Part A2 SD Host Controller Version 3.00

- SDA Part 1 Physical Layer Specification Version 3.00

- SDA Part E1 SDIO Specification Version 3.00

- JEDEC eMMC Specification Version 4.51

- AMBA, AHB Specification Version 2.00

- AMBA, Advanced Extensible Interface (AXI) Specification Version 1.00 (Optional)

- Open Core Protocol (OCP) Specification Version 2.2 (Optional)

- The core supports:

- 32-bit and 64-bit system data bus

- Interrupts and wake up functionality

- Internal Clock divider for various card operational modes

- One of the AHB, AXI or OCP System/Host bus

- The data is transferred using:

- Programmed Input/Output (PIO) mode on the Host Bus Slave interface

- Direct Memory Access (DMA) on the Host Bus Master interface\*

- Configurable FIFO size to support different block sizes.

Note: The Host Bus is AHB or AXI or OCP.

- UHS-I features (SD3.0/SDIO3.0) supports:

- 1.8V voltages switch operation

- Tuning for SDR104 mode and SDR50

- Host clock rate variable between 0 and 208 MHz

- Up to 832 Mbps data rate using 4 parallel data lines (SDR104 mode)

- Transfers the data in 1-bit and 4-bit SD modes and SPI mode

- Transfers the data in SDR104, DDR50, SDR50, SDR25, SDR12, DS and HS modes

- Cyclic Redundancy Check (CRC): CRC7 for commands, CRC16 for data integrity

- Variable-length data transfers

- Performs Read Wait Control, Suspend/Resume operation with SDIO CARD

- Designed to work with I/O cards, Read-only cards and Read/Write cards

- Card Detection (Insertion/Removal)

#### eMMC 4.51 features:

- eMMC 4.51 security protocol commands

- Primary and alternate boot modes

- Packed commands, Data Tags, Discard and Sanitize features

- 4KB block support

- Tuning for HS200 mode

- MMC Plus and MMC Mobile

- Host clock rate variable between 0 and 200 MHz

- Up to 1.6Gbps (HS200) data rate using 8 bit parallel data lines

- Transfers the data in 1-bit, 4-bit and 8-bit modes

- CRC7 for command and CRC16 for data integrity

- Password protection of cards

## 2.3 Architecture

# 2.3.1 Functional Description

The Arasan SD 3.0/SDIO 3.0/ eMMC 4.51 Host Controller is a Host Controller with an AHB/AXI/OCP processor interface. This product conforms to SD Host Controller Standard Specification Version 3.00. It is also compliant to eMMC 4.51 Specification from JEDEC.

The SD3.0/SDIO3.0/eMMC4.51 Host Controller handles SDIO/SD Protocol at transmission level, packing data, adding CRC, Start/End bit, and checking for transaction format correctness. The Host Controller provides Programmed IO method and DMA data transfer method. In programmed IO method, the Host processor transfers data using the Buffer Data Port Register.

The SD3.0/SDIO3.0/eMMC4.51 Host Controller support for DMA can be determined by checking the DMA support in the Capabilities register. DMA allows a peripheral to read or write memory without the intervention from the CPU. This Host Controller's Host

Controller system address register points to the first data address, and data is then accessed sequentially from that address. It supports connection to a single slot and performs multi-block writes and erases the lower access.

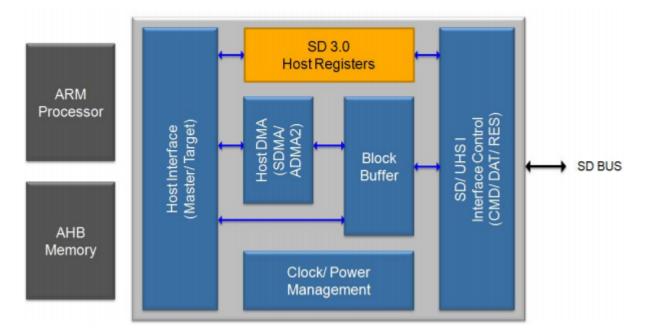

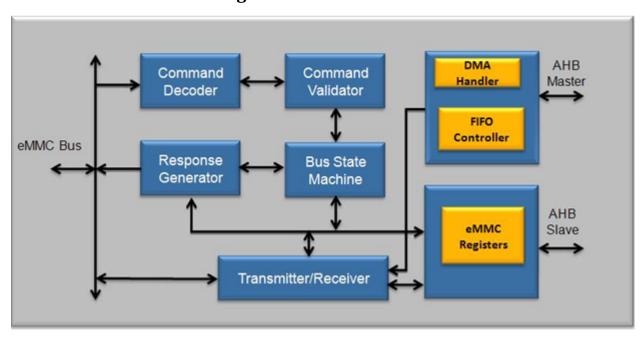

## 2.3.2 Functional Block Diagram

Figure 2: eMMC5.1/SD3.0/SDIO3.0 Host Controller Functional Block Diagram

## 2.3.3 Functional Block Diagram Description

## 2.3.3.1 Host Interface (Master/ Target)

The Master Bus Interface is used to access the DMA Controller (when using DMA) or Advanced Direct Memory Access (ADMA2 Modes). The DMA Controller module interfaces with the Host (AHB/AXI/OCP) Master Module to generate Transfers and on the other side it interfaces with the Block Buffer to store/fetch block data. The DMA Controller implements a separate DMA for Simple Direct Memory Access (SDMA) Operation and Separate DMA for the ADMA2 Operation. In addition, it implements Host Transaction Generator that generates controls for the Host Master Interface Module.

The DMA Controller uses the Master DMA interfaces to transfer data between the Host Controller and the System Memory and vice-versa and also to fetch the descriptors while operating in ADMA2 mode.

The Host Controller interfaces with the System bus using the AHB, AXI, or OCP Master and Slave Interface. The Slave Interface is used to access the Registers inside the Host controller. The Slave Interface supports only single transfer access (no Burst Support) and only one outstanding Read/Write transaction in case of AXI or OCP interface.

#### 2.3.3.2 Host DMA

The PIO/DMA Controller module implements the SDMA and ADMA2 engines as defined in the SD Host Controller specification and maintains the block transfer counts for PIO operation. It interacts with the Registers Set and starts the DMA engine when a Command with Data Transfer is involved.

The DMA Controller interfaces with the Host (AHB/AXI/OCP) Master module to generate Transfers and on the other side it interfaces with the Block Buffer to store/fetch block data. It implements a separate DMA for SDMA operation and separate DMA for the ADMA2 operation. In addition implements Host Transaction Generator that generates controls for the Host Master interface module.

#### 2.3.3.3 SD 3.0 Host Register

The Host Controller Register Set implements the Registers defined by the SD Host Controller Specification. The Registers are Byte/DWORD accessible from the Slave interface. The Host Controller Register Set also implements the Data Port Registers for the PIO Mode transfers.

The SD/SDIO Host Controller uses a Dual Port Block Buffer (read/write on both ports) that is used to store the Block Data during SD Transfers. The size of the Block Buffer is Configurable and has to be a mini mum of 1 Block Size (Block Size is 512 Bytes in SD Memory and up to 2K Bytes in SDIO).

The Register Set provides the control signals and monitors the status signals from the blocks to set Interrupt Status Bits and eventually generate Interrupt signal to the Host Bus.

#### 2.3.3.4 Block Buffer

The SD/SDIO Host Controller uses a Dual Port Block Buffer (Read/Write on both ports) or a Two Port (One Read/One Write) that is used to store the Block Data during SD Transfers. The size of the Block Buffer is Configurable and has to be a minimum of 1 Block Size (Block Size is 512 Bytes in SD Memory and up to 2K Bytes in SDIO).

To achieve maximum performance the Block buffer has to be sized to twice the maximum Block Size supported by Host Controller. The Block Buffer uses Circular Buffer Architecture. One side of the Block Buffer is interfaced with the DMA Controller and operates on the Host Clock. The other side of the Block Buffer interfaces with SD Interface Control Logic and operates on SD Clock. During a write transaction (data transferred from a Host Processor to SD3.0/SDIO3.0/ eMMC 4.51 card), the data is fetched from the Host System Memory and is stored in the Block Buffer. When a Block of data is available, the SD Control logic will transfer it onto the SD Interface.

The DMA Controller continues to fetch additional block of data when the Block Buffer has space. During a Read transaction (data transferred from SD3.0/SDIO3.0/ eMMC 4.51 card to Host Processor), the data from SD3.0/SDIO3.0/ eMMC 4.51 card will be written in to Block Buffer and at the end when the CRC of the Block is valid, the data is committed. When a Block of data is available, then the DMA Controller transfers this data to the Host System Memory. The SD Interface Control logic meanwhile receives the next Block of data provided there is space in the Block Buffer. If the

Host controller cannot accept any data from SD3.0/SDIO3.0/ eMMC 4.51 card, then it will issue Read Wait (if card supports Read Wait mechanism) to stop the data transfer from card or by stopping the clock.

**Note**: FIFO depth can be varied using parameter passed to the Core using the 'dot parameter instantiation'. When the Block Buffer size is twice that of the Block Size, the Block Buffer behaves like a ping-pong buffer.

## 2.3.3.5 SD (UHS - I) Interface Control (CMD/ DAT/ RES)

The SD Interface Control block maps the internal signals to the External SD Interface and vice versa. Based on the Bus Width (1/4/8) the internal signals are driven out appropriately. In case of DS, the outputs are driven on the negative edge of the sd\_clk.

The input from RxFlops module are latched on the rx\_clk (looped back or tuned clock) and is output to the Receive Control Module for further processing.

#### 2.3.3.6 Clock/ Power Management

The SD Interface Clock Generator module generates the SD Clock from the Reference Clock (xin\_clk), based on the Controls programmed in the Clock Control Register. These include the Clock Divide Value, Clock Enable and so on. The outputs from this module are the SD\_CLK and the CARD Clock. The SD\_CLK is used by the eMMC/SD Interface Control Logic and the CARD Clock connected to the "CLK" Pin on the EMMC Interface. This module also generates system resets to various clock domains.

# 2.4 Pinouts

## 2.4.1 I/O Description

The Arasan SD3.0/SDIO3.0/ eMMC 4.51 Host Controller has the following interface groups.

- System (AHB/AXI/OCP) Bus Interface Signals

- SD3.0/SDIO3.0/ eMMC 4.51 Interface that forms the main card interface

- Power Control Signals

- Clock, Special Controls and Test Mode Signals

- Block RAM, Static Random Access Memory (SRAM) Interface Signals

- Core Configuration Signals

**Table 1: AHB Bus Interface Signals**

| Pin                      | Direction | Description                       |

|--------------------------|-----------|-----------------------------------|

| ahb_clk                  | In        | AHB System Clock                  |

| ahb_reset_n              | In        | AHB System Reset (Active Low)     |

| ahbmaster_hbusreq        | Out       | AHB Bus request                   |

| ahbmaster_hgrant         | In        | AHB Bus Grant                     |

| ahbmaster_haddr[AW-1:0]  | Out       | DWord Address                     |

| ahbmaster_hwdata[DW-1:0] | Out       | AHB master write data             |

| ahbmaster_hrdata[DW-1:0] | In        | AHB master read data              |

| ahbmaster_hwrite         | Out       | Write / Read Direction Indication |

| ahbmaster_hsize[2:0]     | Out       | Size (byte, half word or word)    |

| ahbmaster_hburst[2:0]    | Out       | Burst Size                        |

| ahbmaster_hready         | In        | Ready signal                      |

| ahbmaster_htrans[1:0]    | Out       | Transfer type                     |

| ahbmaster_hresp[1:0]     | In        | Transfer response                 |

| ahb_intr                 | Out       | Interrupt to the ARM              |

| ahb_wkup                 | Out       | Wakeup Indication to ARM          |

| ahbtarget_hsel           | In        | Slave Select                      |

| ahbtarget_haddr[15:0]    | In        | DWord Address (256 bytes)         |

| ahbtarget_hwdata[31:0]   | In        | Write Data                        |

| ahbtarget_hrdata[31:0]   | Out       | Read Data                         |

| ahbtarget_hwrite         | In        | Write / Read Direction Indication |

| ahbtarget_hsize[2:0]     | In        | Size (Byte, Half Word or Word)    |

| ahbtarget_htrans[1:0]    | In        | Transfer Type                     |

| ahbtarget_hready_in      | In        | Slave Ready Input                 |

| ahbtarget_hready         | Out       | Slave Ready                       |

| ahbtarget_hresp[1:0]     | Out       | Transfer Response                 |

Note: Target interface doesn't support BURST transaction.

**Table 2: OCP Bus Interface Signals**

| Pin                     | Direction | Description                                        |

|-------------------------|-----------|----------------------------------------------------|

| clk_ocp                 | In        | OCP System Clock.                                  |

| OCPMaster_MAddr[AW-1:0] | Out       | OCP Master read/write address.                     |

| OCPMaster_MCmd[2:0]     | Out       | Indicates the type of transaction that the OCP     |

|                         |           | Master has initiated                               |

| OCPMaster_MData[DW-1:0] | Out       | Write data from OCP Master to the slave            |

| OCPMaster_MDataValid    | Out       | Is the qualifier for OCPMaster_MData               |

|                         | In        | Indicates that the OCP Slave has accepted the      |

|                         |           | command                                            |

| OCPMaster_SData[DW-1:0] | In        | Read data from OCP Slave                           |

| OCPMaster_SDataAccept   | In        | Asserted by OCP slave to indicate that the current |

|                         |           | Master write data is accepted                      |

| OCPMaster_SResp[1:0]        | In  | Response signal for Master write transfers       |

|-----------------------------|-----|--------------------------------------------------|

| OCPMaster_MByteEn[          | Out | Byte enable from the Master for write/read       |

| 3:0]                        |     | transactions                                     |

| OCPMaster_MBurstLength[4:0] | Out | Indicates the burst length of the transaction    |

| OCPMaster_MBurstPrecise     | Out | Indicates that the given burst length is precise |

| OCPMaster_MBurstSeq         | Out | Indicates the type of burst                      |

| [2:0]                       |     |                                                  |

| OCPMaster_MBurstSingleReq   | Out | Indicates the number of requests associated with |

|                             |     | the burst                                        |

| OCPMaster_MDataLast         | Out | Last Data of the burst                           |

| OCPMaster_MReqLast          | Out | Last request in a burst                          |

| OCPMaster_SRespLast         | In  | Last response in a burst                         |

| OCPMaster_MDataByteEn[3:0]  | Out | Write Byte enables the OCP slave during Data     |

|                             |     | handshake phase                                  |

| OCPMaster_max_burst_size_c  | In  | Configurable burst length                        |

| onfig                       |     |                                                  |

| OCPSlave_MCmd[2:0]          | In  | Type of transaction from the Master              |

| OCPSlave_MAddr[31:0]        | In  | Transfer address from Master                     |

| OCPSlave_MData[31:0]        | In  | Write data from OCP Master                       |

| OCPSlave_SCmdAccept         | Out | Acceptance signal to the external OCP Master for |

|                             |     | the request phase                                |

| OCPSlave_SResp[1:0]         | Out | Response signal from OCP Slave                   |

| OCPSlave_SData[31:0]        | Out | Read data from OCP Slave                         |

| OCPSlave_MByteEn[3:0]       | In  | Byte Enable from OCP Master                      |

| OCPSlave_MReset_n           | In  | Reset signaling from OCP Master                  |

| OCPSlave_MRespAccept        | In  | Master accepts response                          |

**Table 3: AXI Bus Interface Signals**

| Pin                   | Direction | Description                                                                              |

|-----------------------|-----------|------------------------------------------------------------------------------------------|

| aximst_arid[3:0]      | Out       | Read address ID. This signal is the identification tag                                   |

|                       |           | for the read address group of signals.                                                   |

| aximst_araddr[AW-1:0] | Out       | Read address. The read address bus gives the initial                                     |

|                       |           | address of a read burst transaction. Only the start                                      |

|                       |           | address of the burst is provided and the control                                         |

|                       |           | signals that are issued alongside the address detail                                     |

|                       |           | how the address is calculated for the remaining transfers in the burst                   |

| aximst_arlen[3:0]     | Out       | Burst length. The burst length gives the exact                                           |

|                       | Out       | number of transfers in a burst. This information                                         |

|                       |           | determines the number of data transfers associated                                       |

|                       |           | with the address.                                                                        |

| aximst_arsize[2:0]    | Out       | Burst size. This signal indicates the size of each                                       |

|                       |           | transfer in the burst.                                                                   |

| aximst_arburst[1:0]   | Out       | Burst type. The burst type, coupled with the size                                        |

|                       |           | information, details how the address for each                                            |

|                       |           | transfer within the burst is calculated.                                                 |

| aximst_arvalid        | Out       | Read address valid. This signal indicates, when HIGH,                                    |

|                       |           | that the read address and control information is                                         |

|                       |           | valid and will remain stable until the address                                           |

|                       |           | acknowledge signal, ARREADY, is high.                                                    |

|                       |           | 1 = address and control information valid 0 = address and control information not valid. |

| aximst_rid[3:0]       | In        | Read ID tag. This signal is the ID tag of the read data                                  |

| axiiist_iiu[3.0]      | ""        | group of signals. The RID value is generated by the                                      |

|                       |           | slave and must match the ARID value of the read                                          |

|                       |           | transaction to which it is responding.                                                   |

| aximst_rdata[DW-1:0]  | In        | Read data.                                                                               |

| aximst_rresp[1:0]     | In        | Read response. This signal indicates the status of the                                   |

|                       |           | read transfer. The allowable responses are OKAY,                                         |

|                       |           | EXOKAY, SLVERR, and DECERR.                                                              |

| aximst_rlast          | In        | Read last. This signal indicates the last transfer in a                                  |

|                       |           | read burst.                                                                              |

| aximst_rvalid         | In        | Read valid. This signal indicates that the required                                      |

|                       |           | read data is available and the read transfer can                                         |

|                       |           | complete:                                                                                |

|                       |           | 1 = read data available 0 = read data not available                                      |

| aximst_rready         | Out       | Read ready. This signal indicates that the Master can                                    |

| axiiiist_iieauy       | Out       | accept the read data and response information:                                           |

|                       |           | 1= Master ready                                                                          |

|                       |           | 0 = Master not ready.                                                                    |

| axislv_awid[7:0]      | In        | Write address ID. This signal is the identification tag                                  |

|                       |           | for the write address group of signals.                                                  |

| Pin                    | Direction | Description                                                            |

|------------------------|-----------|------------------------------------------------------------------------|

| axislv_awaddr[AW-1:0]  | In        | Write address. The write address bus gives the                         |

|                        |           | address of the first transfer in a write burst                         |

|                        |           | transaction. The associated control signals are used                   |

|                        |           | to determine the addresses of the remaining                            |

|                        |           | transfers in the burst.                                                |

| axislv_awlen[3:0]      | In        | Burst length. The burst length gives the exact                         |

|                        |           | number of transfers in a burst. This information                       |

|                        |           | determines the number of data transfers associated                     |

|                        |           | with the address.                                                      |

| axislv_awsize[2:0]     | In        | Burst size. This signal indicates the size of each                     |

|                        |           | transfer in the burst. Byte lane strobes indicate                      |

|                        |           | exactly which byte lanes to update.                                    |

| axislv_awburst[1:0]    | In        | Burst type. The burst type, coupled with the size                      |

|                        |           | information, details how the address for each                          |

|                        |           | transfer within the burst is calculated.                               |

| axislv_awvalid         | In        | Write address valid. This signal indicates that valid                  |

| _                      |           | write address and control information are available:                   |

|                        |           | 1 = address and control information available                          |

|                        |           | 0 = address and control information not available                      |

|                        |           | The address and control information remain stable                      |

|                        |           | until the address acknowledge signal, AWREADY,                         |

|                        |           | goes HIGH.                                                             |

| axislv_awready         | Out       | Write address ready. This signal indicates that the                    |

| _ ,                    |           | slave is ready to accept an address and associated                     |

|                        |           | control signals:                                                       |

|                        |           | 1 = slave ready                                                        |

|                        |           | 0 = slave not ready.                                                   |

| axislv_wid[7:0]        | In        | Write ID tag. This signal is the ID tag of the write                   |

|                        |           | data transfer. The WID value must match the AWID                       |

|                        |           | value of the write transaction.                                        |

| axislv_wdata[DW-1:0]   | In        | Write data.                                                            |

| axislv_wstrb[DW/8-1:0] | In        | Write strobes. This signal indicates which byte lanes                  |

|                        |           | to update in memory. There is one write strobe for                     |

|                        |           | each eight bits of the write data bus. Therefore,                      |

|                        |           | WSTRB[n] corresponds to WDATA[(8 \( \bar{p} \) n) + 7:(8 \( \bar{p} \) |

|                        |           | n)].                                                                   |

| axislv_wlast           | In        | Write last. This signal indicates the last transfer in a               |

|                        |           | write burst.                                                           |

| axislv wvalid          | In        | Write valid. This signal indicates that valid write data               |

|                        |           | and strobes are available:                                             |

|                        |           | 1 = write data and strobes available                                   |

|                        |           | 0 = write data and strobes not available.                              |

| axislv_wready          | Out       | Write ready. This signal indicates that the slave can                  |

|                        |           | accept the write data:                                                 |

|                        |           | 1 = slave ready                                                        |

|                        |           | 1 Stare reday                                                          |

| Pin                   | Direction | Description                                                                                            |

|-----------------------|-----------|--------------------------------------------------------------------------------------------------------|

|                       |           | 0 = slave not ready.                                                                                   |

| axislv_bid[7:0]       | Out       | Response ID. The identification tag of the write                                                       |

|                       |           | response. The BID value must match the AWID value                                                      |

|                       |           | of the write transaction to which the slave is                                                         |

|                       |           | responding.                                                                                            |

| axislv_bresp[1:0]     | Out       | Write response. This signal indicates the status of                                                    |

|                       |           | the write transaction. The allowable responses are                                                     |

|                       |           | OKAY, EXOKAY, SLVERR, and DECERR.                                                                      |

| axislv_bvalid         | Out       | Write response valid. This signal indicates that a                                                     |

|                       |           | valid write response is available:                                                                     |

|                       |           | 1 = write response available                                                                           |

|                       |           | 0 = write response not available.                                                                      |

| axislv_bready         | In        | Response ready. This signal indicates that the                                                         |

|                       |           | Master can accept the response information.                                                            |

|                       |           | 1 = Master ready                                                                                       |

|                       |           | 0 = Master not ready                                                                                   |

| axislv_arid[7:0]      | In        | Read address ID. This signal is the identification tag                                                 |

|                       |           | for the read address group of signals.                                                                 |

| axislv_araddr[31:0]   | In        | Read address. The read address bus gives the initial                                                   |

|                       |           | address of a read burst transaction. Only the start                                                    |

|                       |           | address of the burst is provided and the control                                                       |

|                       |           | signals that are issued alongside the address detail                                                   |

|                       |           | how the address is calculated for the remaining                                                        |

|                       |           | transfers in the burst.                                                                                |

| axislv_arlen[3:0]     | In        | Burst length. The burst length gives the exact                                                         |

|                       |           | number of transfers in a burst. This information                                                       |

|                       |           | determines the number of data transfers associated                                                     |

|                       | l         | with the address.                                                                                      |

| axislv_arsize[2:0]    | In        | Burst size. This signal indicates the size of each                                                     |

| avialis aubsurat[1:0] | l a       | transfer in the burst.                                                                                 |

| axislv_arburst[1:0]   | In        | Burst type. The burst type, coupled with the size                                                      |

|                       |           | information, details how the address for each transfer within the burst is calculated.                 |

| aviely emplied        | lo.       |                                                                                                        |

| axislv_arvalid        | In        | Read address valid. This signal indicates, when HIGH, that the read address and control information is |

|                       |           | valid and will remain stable until the address                                                         |

|                       |           | acknowledge signal, ARREADY, is high.                                                                  |

|                       |           | 1 = address and control information valid                                                              |

|                       |           | 0 = address and control information valid.                                                             |

| axislv_arready        | Out       | Read address ready. This signal indicates that the                                                     |

| anisiv_arready        | Jul       | slave is ready to accept an address and associated                                                     |

|                       |           | control signals:                                                                                       |

|                       |           | 1 = slave ready                                                                                        |

|                       |           | 0 = slave neady.                                                                                       |

| avisly rid[7:0]       | Out       | Read ID tag. This signal is the ID tag of the read data                                                |

| axislv_rid[7:0]       | Uut       | wear in rag. This signal is the in rag of the read data                                                |

| Pin                | Direction | Description                                             |

|--------------------|-----------|---------------------------------------------------------|

|                    |           | group of signals. The RID value is generated by the     |

|                    |           | slave and must match the ARID value of the read         |

|                    |           | transaction to which it is responding.                  |

| axislv_rdata[31:0] | Out       | Read data. The read data bus can be 8, 16, 32, 64,      |

|                    |           | 128, 256, 512, or 1024 bits wide.                       |

| axislv_rresp[1:0]  | Out       | Read response. This signal indicates the status of the  |

|                    |           | read transfer. The allowable responses are OKAY,        |

|                    |           | EXOKAY, SLVERR, and DECERR.                             |

| axislv_rlast       | Out       | Read last. This signal indicates the last transfer in a |

|                    |           | read burst.                                             |

| axislv_rvalid      | Out       | Read valid. This signal indicates that the required     |

|                    |           | read data is available and the read                     |

|                    |           | transfer can complete:                                  |

|                    |           | 1 = read data available                                 |

|                    |           | 0 = read data not available.                            |

| axislv_rready      | In        | Read ready. This signal indicates that the Master can   |

|                    |           | accept the read data and response information:          |

|                    |           | 1= Master ready                                         |

|                    |           | 0 = Master not ready.                                   |

| int_to_arm         | Out       | Interrupt to the ARM                                    |

| cfg_mstid          | In        | Programmable ID for Master interface                    |

Table 4: SD3.0/SDIO3.0/eMMC4.51 Interface

| Pin          | Direction | Description                                           |

|--------------|-----------|-------------------------------------------------------|

| sdif_cd_n    | In        | Active Low. Card Detection for single Slot (optional. |

|              |           | Used for SD/SDIO interface only)                      |

| sdif_wp      | In        | Active High. SD Card Write Protect (optional. Used    |

|              |           | for SD/SDIO Interface only)                           |

| sdif_clkout  | Out       | Clock to Card (CLK)                                   |

| rxclk_in     | In        | Clock looped back from PAD                            |

| sdif_cmdin   | In        | Command Input                                         |

| sdif_cmdout  | Out       | Command Output                                        |

| sdif_cmdena  | Out       | Command Output Enable                                 |

| sdif_dat0in  | In        | Data0 Input                                           |

| sdif_dat0out | Out       | Data0 Output                                          |

| sdif_dat0en  | Out       | Data0 Output Enable                                   |

| sdif_dat1in  | In        | Data1 Input or Interrupt (for SDIO)                   |

| sdif_dat1out | Out       | Data1 Output                                          |

| sdif_dat1en  | Out       | Data1 Output Enable                                   |

| sdif_dat2in  | In        | Data2 Output or Read Wait (optional)                  |

| sdif_dat2out | Out       | Data2 Output                                          |

| sdif_dat2en  | Out       | Data2 Output Enable                                   |

| sdif_dat3in  | In        | Data3 Input                                           |

| Pin          | Direction | Description         |

|--------------|-----------|---------------------|

| sdif_dat3out | Out       | Data3 Output        |

| sdif_dat3en  | Out       | Data3 Output Enable |

| sdif_dat4in  | In        | Data4 Input         |

| sdif_dat4out | Out       | Data4 Output        |

| sdif_dat4en  | Out       | Data4 Output Enable |

| sdif_dat5in  | In        | Data5 Input         |

| sdif_dat5out | Out       | Data5 Output        |

| sdif_dat5en  | Out       | Data5 Output Enable |

| sdif_dat6in  | In        | Data6 Input         |

| sdif_dat6out | Out       | Data6 Output        |

| sdif_dat6en  | Out       | Data6 Output Enable |

| sdif_dat7in  | IN        | Data7 Input         |

| sdif_dat7out | Out       | Data7 Output        |

| sdif_dat7en  | Out       | Data7 Output Enable |

**Note:** CMD/DATA output enables are active high signals

Table 5: Power Control Signals (Used for SD/SDIO Mode only)

| Pin                      | Direction | Description                                        |

|--------------------------|-----------|----------------------------------------------------|

| sdhc_ledcontrol          | Out       | LED ON: To Caution the user not to remove the card |

|                          |           | while the SD card is being accessed.               |

| sdhc_sdbuspower          | Out       | Control SD Card Power Supply.                      |

| sdhc_sdbusvoltage[2:0]   | Out       | SD Bus voltage select.                             |

| sdhc_1p8vsigenable       | Out       | 1.8V Signaling Enable                              |

| sdhc_driverstrength[1:0] | Out       | Driver Strength Select                             |

|                          |           | 00b Driver Type B is Selected                      |

|                          |           | 01b Driver Type A is Selected                      |

|                          |           | 10b Driver Type C is Selected                      |

|                          |           | 11b Driver Type D is Selected                      |

**Table 6: Clock, Special Controls and Test Mode Signals**

| Pin                 | Direction | Description                                                                                                                                                                                                                                                                                                 |

|---------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xin_clk             | In        | This clock input is used to generate eMMC/SD Clock. For maximum efficiency this should be around 200 MHz for eMMC or 208MHz (for SD3.0).                                                                                                                                                                    |

| corectrl_itapdlyena | In        | Used to enable selective Tap delay line on the Looped back eMMC/SD Clock (rxclk_in). This signal along with the corectrl_itapdlysel[4:0] selects the amount of delay to be inserted on the line.  When Tuning is enabled (for HS200/SDR104), this signal is ignored and internal controls are used instead. |

| Pin                      | Direction | Description                                              |

|--------------------------|-----------|----------------------------------------------------------|

|                          |           | This should not be asserted when operating in DS         |

|                          |           | mode.                                                    |

| corectrl_itapdlysel[4:0] | In        | Selects one of the 32 Taps on the rxclk_in line. This is |

|                          |           | effective only when corectrl_itapdlyena is asserted      |

|                          |           | and Tuning is not enabled.                               |

| corectrl_itapchgwin      | In        | This is used to gate the output of the Tap Delay lines   |

|                          |           | so as to avoid glitches being propagated into the        |

|                          |           | Core. This signal should be asserted few clocks          |

|                          |           | before the corectrl_itapdlysel changes and should        |

|                          |           | be asserted for few clocks after.                        |

| corectrl_otapdlyena      | In        | Used to enable the selective Tap delay on the            |

|                          |           | card_clk so as to generate the delayed card_clk. This    |

|                          |           | is used to latch the CMD/DAT outputs to generate         |

|                          |           | delay on them w.r.t CLK going out. This signal along     |

|                          |           | with corectrl_otapdlysel[3:0] selects the amount of      |

|                          |           | delay to be inserted on the Clock line.                  |

|                          |           | This signal should not be asserted when operating in     |

|                          |           | DS mode                                                  |

| corectrl_otapdlysel[3:0] | In        | Selects one of the 16 Taps on the sdcard_clk. This is    |

|                          |           | effective only when corectrl_otapdlyena is asserted.     |

| test_mode                | In        | Test mode signal is used for DFT purpose. Muxes in       |

|                          |           | the AXI_reset_n signal for all internally generated      |

|                          |           | resets. (Active High)                                    |

| scan_mode                | In        | Scan Mode signal for selecting Scan Clocks for           |

|                          |           | internally generated clocks                              |

| scan_clk1                | In        | Scan Clock#1 used to mux in for the internally           |

|                          |           | generated sd_clk                                         |

| scan_clk2                | In        | Scan Clock#2 used to mux in for the final rxclk_in       |

|                          |           | (after the tap delay etc)                                |

Table 7: Block RAM (SRAM) Interface Signals

| Pin                   | Direction | Description                                          |

|-----------------------|-----------|------------------------------------------------------|

| sram_clka             | Out       | Clock for PORT A                                     |

| sram_addra [N-1:0]    | Out       | Address bus for PORT A.                              |

|                       |           | The width of the Address bus is based on the size of |

|                       |           | the SRAM (SDHC_BUFFER_SIZE)                          |

| sram_writea           | Out       | Write Enable for PORT A                              |

| sram_reada            | Out       | Read Enable for PORT A                               |

| sram_wrdata[DW-1:0]   | Out       | Write Data for PORT A.                               |

| sram_rddataa [DW-1:0] | In        | Read Data from SRAM on PORT A. N is based on the     |

|                       |           | SDHC_MSTAXI_DW parameter                             |

| sram_clkb             | Out       | Clock for PORT B                                     |

| sram_addrb [N-1:0]    | Out       | Address bus for PORT B.                              |

|                       |     | The width of the Address bus is based on the size of the SRAM (SDHC_BUFFER_SIZE) |

|-----------------------|-----|----------------------------------------------------------------------------------|

| sram_writeb           | Out | Write Enable for PORT B                                                          |

| sram_readb            | Out | Read Enable for PORT B                                                           |

| sram_wrdatab [DW-1:0] | Out | Write Data for PORT B.                                                           |

| sram_rddatab [DW-1:0] | In  | Read Data from SRAM on PORT B.                                                   |

**Table 8: Core Configuration Signals**

| Pin                         | Direction | Description                                                                                                                                                                                              |

|-----------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| corecfg_tuningcount[5:0]    | In        | Configures the Number of Taps (Phases) of the rxclk_in that is supported. The Tuning State machine uses this information to select one of the Taps (Phases) of the rxclk_in during the Tuning Procedure. |

| corecfg_timeoutclkfreq[5:0] | In        | Timeout Clock Frequency Suggested Value is 1. (KHz or MHz). Internally the 1msec /1usecTimer is used for Timeout Detection. The 1msec Timer is generated from the xin_clk.                               |

| corecfg_timeoutclkunit      | In        | Timeout Clock Unit Suggested value is 1'b1 to Select MHz Clock.                                                                                                                                          |

| corecfg_baseclkfreq[7:0]    | In        | Base Clock Frequency for SD Clock. This is the frequency of the xin_clk.                                                                                                                                 |

| corecfg_maxblklength[1:0]   | In        | Max Block Length Maximum Block Length supported by the Core/Device 00: 512 (Bytes) 01: 1024 10: 2048 11: Reserved                                                                                        |

| corecfg_8bitsupport         | In        | 8-bit Support for Embedded Device Suggested Value is 1'b1 (The Core supports 8-bit Interface). Optionally can be set to 1'b0 if the Application supports only 4-bit SD Interface.                        |

| corecfg_adma2support        | In        | ADMA2 Support Suggested Value is 1'b1 (The ADMA2 is supported by Core). Optionally can be set to 1'b0 if the application doesn't want to support ADMA2 Mode                                              |

| corecfg_highspeedsupport    | In        | High Speed Support Suggested Value is 1'b1 (The High Speed mode is supported by Core).                                                                                                                   |

| corecfg_sdmasupport         | In        | SDMA Support Suggested Value is 1'b1 (The SDMA is supported by Core).                                                                                                                                    |

| Pin                      | Direction | Description                                          |

|--------------------------|-----------|------------------------------------------------------|

|                          |           | Optionally can be set to 1'b0 if the application     |

|                          |           | doesn't want to support SDMA Mode                    |

| corecfg_suspressupport   | In        | Suspend/Resume Support                               |

|                          |           | Suggested Value is 1'b1 (The Suspend/Resume is       |

|                          |           | supported by Core).                                  |

|                          |           | Optionally can be set to 1'b0 if the application     |

|                          |           | doesn't want to support Suspend/Resume Mode          |

| corecfg_3p3voltsupport   | In        | 3.3V Support                                         |

|                          |           | Suggested Value is 1'b1 as the 3.3 V is the default  |

|                          |           | voltage on the SD Interface.                         |

| corecfg_3p0voltsupport   | In        | 3.0V Support Should be set based on whether 3.0V is  |

|                          |           | supported on the SD Interface.                       |

| corecfg_1p8voltsupport   | In        | 1.8V Support                                         |

|                          |           | Suggested Value is 1'b1 (The 1.8 Volt Switching is   |

|                          |           | supported by Core). Optionally can be set to 1'b0 if |

|                          |           | the application doesn't want 1.8V switching (SD3.0)  |

| corecfg_64bitsupport     | In        | 64-bit System Bus Support                            |

|                          |           | This should be set based on the System Address Bus.  |

|                          |           | When set to 1'b0 the Core supports only 32-bit       |

|                          |           | System Bus. When set to 1'b1 the Core supports 64-   |

|                          |           | bit System Address.                                  |

| corecfg_asyncintrsupport | In        | Asynchronous Interrupt Support                       |

|                          |           | Suggested Value is 1'b1 (The Core supports           |

|                          |           | monitoring of Asynchronous Interrupt)                |

| corecfg_slottype[1:0]    | In        | Slot Type Should be set based on the final product   |

|                          |           | usage                                                |

|                          |           | 00 - Removable SCard Slot                            |

|                          |           | 01 - Embedded Slot for One Device                    |

|                          |           | 10 - Shared Bus Slot                                 |

|                          |           | 11 – Reserved                                        |

| corecfg_sdr50support     | In        | SDR50 Support                                        |

|                          |           | Suggested Value is 1'b1 (The Core supports SDR50     |

|                          |           | mode of operation)                                   |

|                          |           | Optionally can be set to 1'b0 if the application     |

|                          |           | doesn't want to support SDR50                        |

| corecfg_sdr104support    | In        | SDR104 Support                                       |

|                          |           | Suggested Value is 1'b1 (The Core supports SDR104    |

|                          |           | mode of operation)                                   |

|                          |           | Optionally can be set to 1'b0 if the application     |

|                          |           | doesn't want to support SDR104                       |

| corecfg_ddr50support     | In        | DDR50 Support                                        |

|                          |           | Suggested Value is 1'b1 (The Core supports DDR50     |

|                          |           | mode of operation)                                   |

|                          |           | Optionally can be set to 1'b0 if the application     |

|                          |           | doesn't want to support DDR50                        |

| Pin                           | Direction | Description                                                       |

|-------------------------------|-----------|-------------------------------------------------------------------|

| corecfg_hs400support          | ln        | HS400 Support                                                     |

|                               |           | Suggested Value is 1'b1 (The Core supports HS400                  |

|                               |           | Mode). This applies only to eMMC5.0 mode. This                    |

|                               |           | should be set to 1'b0 for SD3.0 mode Optionally can               |

|                               |           | be set to 1'b0 if the application doesn't want to                 |

|                               |           | support HS400                                                     |

| corecfg_adriversupport        | In        | Driver Type A Support                                             |

|                               |           | This bit should be set based on whether Driver Type               |

|                               |           | A for 1.8 Signaling is supported or not.                          |

| corecfg_cdriversupport        | In        | Driver Type C Support                                             |

|                               |           | This bit should be set based on whether Driver Type               |

|                               |           | C for 1.8 Signaling is supported or not.                          |

| corecfg_ddriversupport        | In        | Driver Type D Support                                             |

|                               |           | This bit should be set based on whether Driver Type               |

|                               |           | D for 1.8 Signaling is supported or not.                          |

| corecfg_retuningtimercnt[3:0] | In        | Timer Count for Re-Tuning                                         |

|                               |           | This is the Timer Count for Re-Tuning Timer for Re-               |

|                               |           | Tuning Mode 1 to 3. Setting to 4'b0 disables Re-                  |

| 6 6                           |           | Tuning Timer.                                                     |

| corecfg_tuningforsdr50        | In        | Use Tuning for SDR50                                              |

|                               |           | This bit should be set if the Application wants Tuning            |

|                               |           | be used for SDR50 Modes. The Core operates with or                |

|                               |           | without tuning for SDR50 mode as long as the Clock                |

|                               | 1         | can be manually tuned using tap delay.                            |

| corecfg_retuningmodes[1:0]    | ln        | Re-Tuning Modes                                                   |

|                               |           | Should be set to 2'b00 as the Core supports only the              |

|                               | 1         | Mode0 Retuning.                                                   |

| corecfg_spisupport            | In        | SPI Mode Support                                                  |

|                               |           | Suggested Value is 1'b1 (The Core supports SPI mode of operation) |

|                               |           | Optionally can be set to 1'b0 if the application                  |

|                               |           | doesn't want to support SPI Mode                                  |

| corecfg_spiblkmode            | In        | SPI Block Mode                                                    |

| corecig_spibikinode           | 111       | Reserved and should be set to1'b0                                 |

| corecfg type4support          | In        | Driver Type 4 Support                                             |

| corecig_type4support          | 111       | This bit should be set to 1'b1 if the Host Controller             |

|                               |           | supports                                                          |

|                               |           | Type4 Drive Strength (eMMC5.0), otherwise it                      |

|                               |           | should be set to 0.                                               |

| corecfg_initpresetval[12:0]   | In        | Preset Value for Initialization.                                  |

| corecfg_dsppresetval[12:0]    | In        | Preset Value for Default Speed                                    |

| corecfg_hsppresetval[12:0]    | In        | Preset Value for High Speed                                       |

| corecfg_sdr12presetval[12:0]  | In        | Preset Value for SDR12                                            |

| corecfg_sdr25presetval[12:0]  | In        | Preset Value for SDR25                                            |

| corecfg_sdr50presetval[12:0]  | In        | Preset Value for SDR50                                            |

| co.co.b_sarsopiesetvai[12.0]  |           | Treate falactor ability                                           |

| Pin                           | Direction | Description                                         |

|-------------------------------|-----------|-----------------------------------------------------|

| corecfg_sdr104presetval[12:0] | In        | Preset Value for SDR104                             |

| corecfg_ddr50presetval[12:0]  | In        | Preset Value for DDR50                              |

| corecfg_hs400presetval[12:0]  | In        | Preset Value for HS400                              |

| corecfg_maxcurrent1p8v[7:0]   | In        | Maximum Current for 1.8V                            |

| corecfg_maxcurrent3p0v[7:0]   | In        | Maximum Current for 3.0V                            |

| corecfg_maxcurrent3p3v[7:0]   | In        | Maximum Current for 3.3V                            |

| corecfg_asyncwkupena          | In        | Determines the Wakeup Signal Generation Mode.       |